Parallel-serial conversion circuit and device applied to high-speed interface physical layer chip

A physical layer chip and high-speed interface technology, applied in the field of high-speed parallel-to-serial conversion design, can solve the problems of internal noise differential signals prone to delay differences, complex circuits, etc., to achieve expanded application range, high-speed parallel-to-serial conversion, simple circuit Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

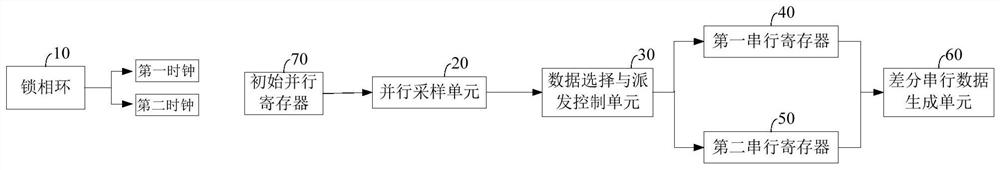

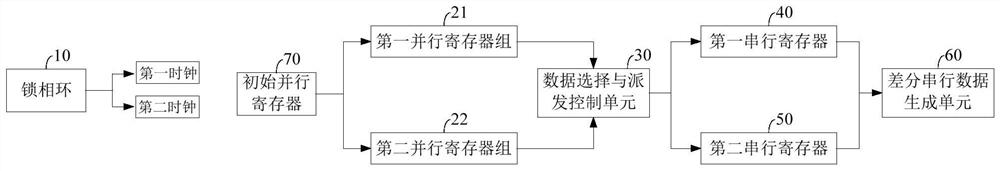

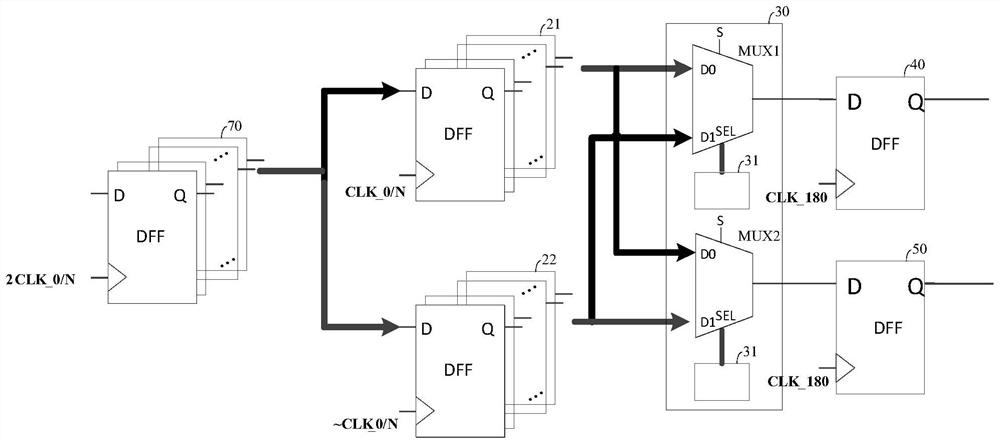

[0018] see Figure 1 to Figure 5 , an embodiment of the present invention provides a parallel-serial conversion circuit applied to a high-speed interface physical layer chip for converting parallel data into differential serial data. The parallel-serial conversion circuit includes: a phase-locked loop 10, a parallel data sampling unit 20. Data selection and distribution control unit 30 , first serial register 40 , second serial register 50 and differential serial data generating unit 60 .

[0019] It is worth noting that if figure 1 As shown in the figure, the embodiment of the present i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com