Method, system and verification platform for verifying chip of system on chip

A system-on-chip, verification platform technology, applied in special data processing applications, instruments, configuration CAD, etc., can solve the problems of high consumption of verification resources and long time spent

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the above objects, features and advantages of the present invention easier to understand, the specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings. Although many specific details are involved in the following explanations, they are intended to allow the application to be fully understood, rather than using them to limit the protection scope of the application.

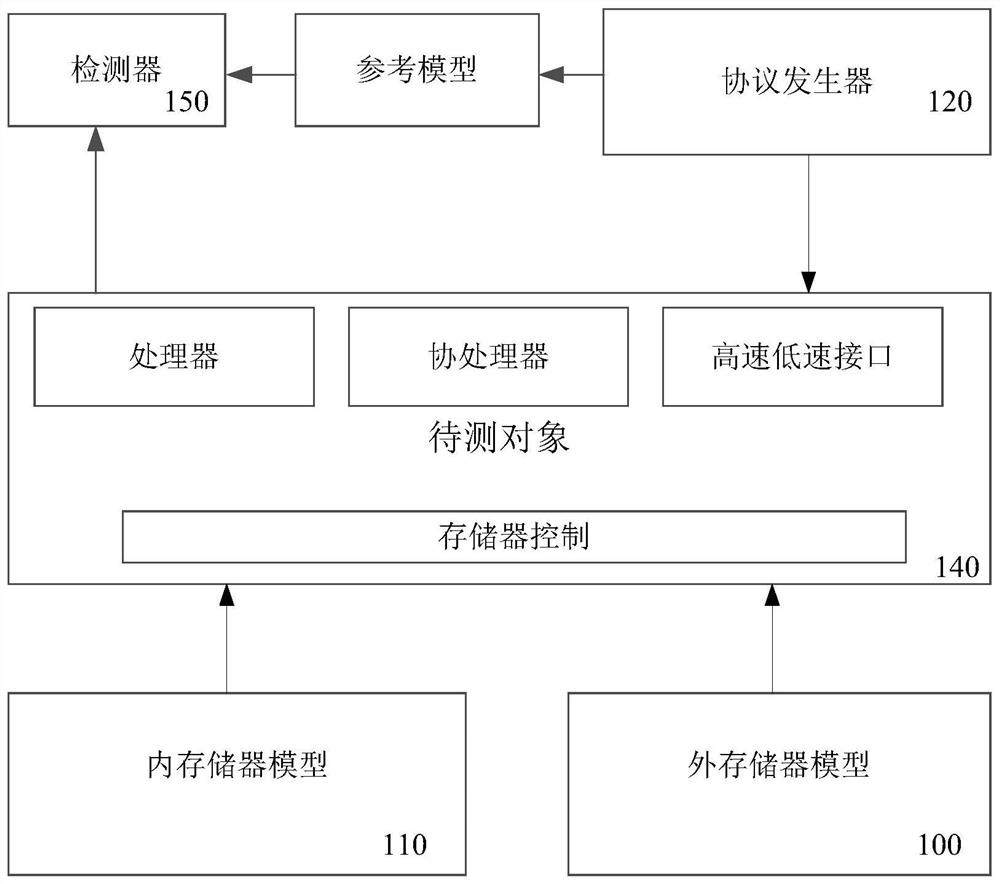

[0021] SoC chips generally include one or more processors (CPUs), various internal and external memories, various hardware acceleration coprocessors for specific business applications, and general high-speed high-speed chips for communicating and exchanging data with other chips or peripherals. and low-speed interfaces, as well as bus interconnection modules that connect these functional units.

[0022] figure 1 The structure of the traditional SoC system-level verification platform based on UVM methodology is i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com