Interconnected bare core interface management system and initialization method thereof

An initialization method and interface management technology, applied in the field of bare core interface management, can solve the problems of unfavorable system rapid construction, difficult design, and time-consuming reconstruction, so as to enhance configuration flexibility, overcome design difficulty, and improve construction speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

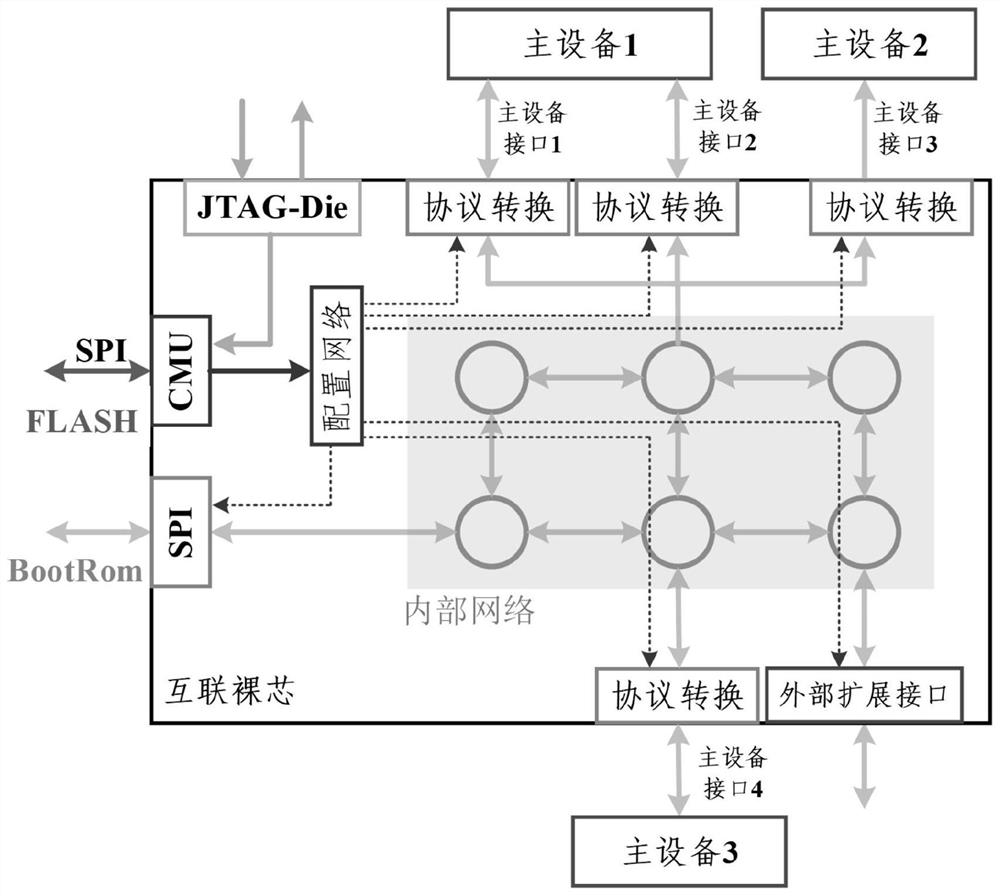

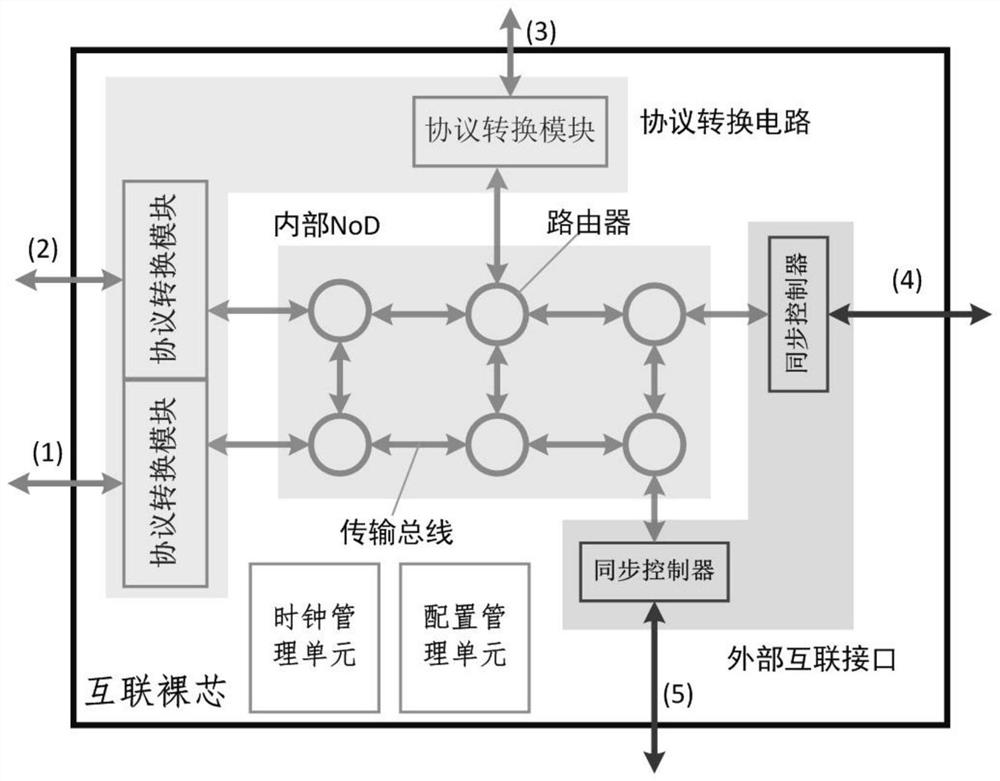

[0038] like figure 1As shown, the interconnected die interface management system includes: a CMU system, a JTAG-Die interface and a configuration network all connected to the CMU system; the CMU system includes a CMU processor and a Flash connected to the CMU processor, the Flash is used to store the software code of the CMU system; the JTAG-Die interface is used to control the startup of the CMU program; one end of the configuration network is connected to the CMU processor in the form of peripherals, and the other end is connected to each interface to be configured through an independent bus ; The CMU processor is used to transmit the configuration data to the function register of each interface to be configured through the configuration network and the independent bus when executing its configuration program, so as to realize the configuration of the interface address translation table.

[0039] The interconnect die interface management system is independent of all other bu...

Embodiment 2

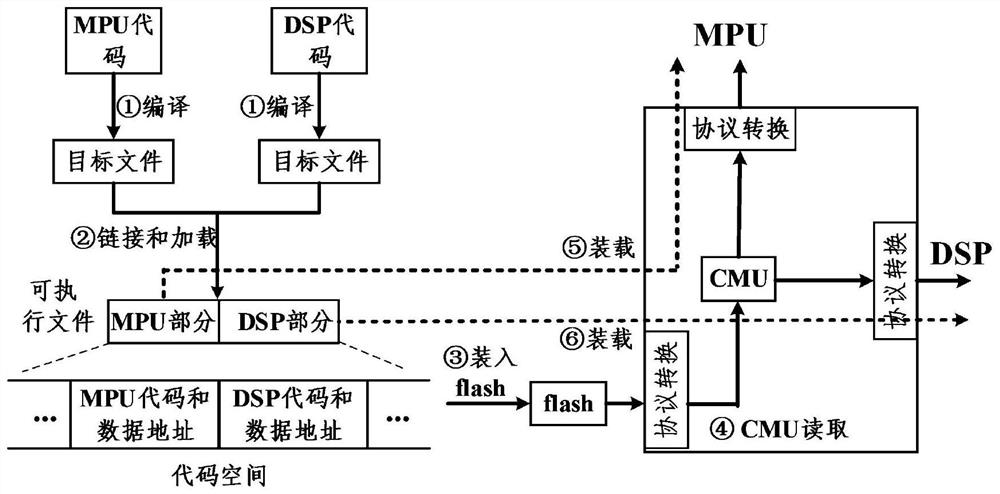

[0045] like figure 2 As shown, the initialization method of the interconnection die interface management system includes the following steps:

[0046] S101, compile the program codes of each master device respectively, and generate the target file;

[0047] S102, link the target file with the startup code provided by the system through the linker, generate an executable file, load the executable file into the specified code space, respectively correspond to the code address space of each master device, and be managed uniformly by the CMU system;

[0048] S103, the codes and data addresses of each master device in the code space are loaded into the program memory Flash of the CMU system respectively;

[0049] S104, start the CMU system through the JTAG-Die interface, load and execute the program in the Flash, generate control signals for each protocol conversion interface, and configure it;

[0050] S105, each master device sequentially reads and executes the startup code th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com