Semiconductor packaging structure and manufacturing method thereof

A packaging structure and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of large chip line loss and thick packaging structure size, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

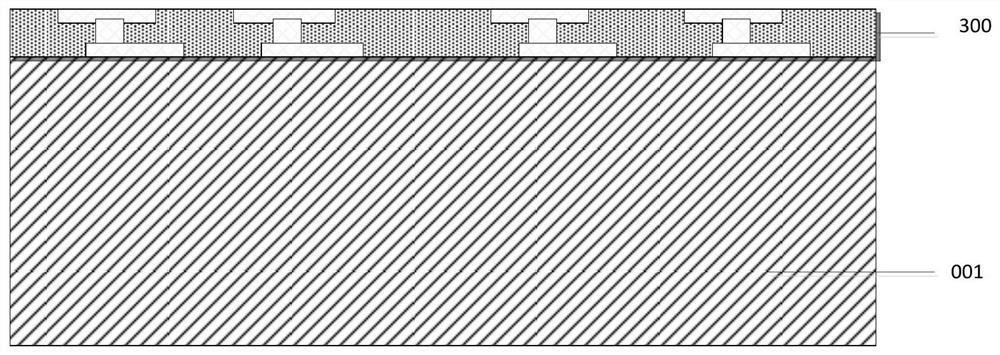

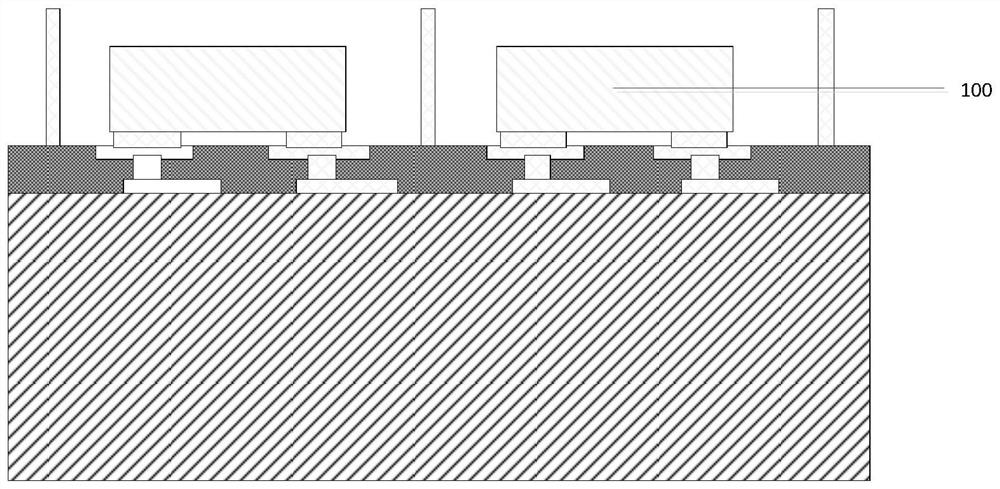

[0034]SeeFigure 1 - Figure 10 This embodiment provides a semiconductor package structure, including:

[0035]The first interconnected structure layer 300.

[0036]The first chip layer, the first chip layer is located on the side surface of the first interconnected structure layer 300, and the first chip layer includes a plurality of first chip 100, and the first chip 100 in the first chip layer is facing the first interconnected structure layer. 300 and electrically connected to the first interconnected structure layer 300;

[0037]The second chip layer, the second chip layer is located on one side surface of the first interconnected structure layer 300, and the second chip layer includes a plurality of second chip 200, the second chip layer in the second chip layer is positive. The first interconnected structure layer 300 is electrically connected to the first interconnected structure layer 300.

[0038]The semiconductor package structure of the present embodiment can achieve the first chip 10...

Embodiment 2

[0051]referenceFigure 11 In this embodiment, another semiconductor package structure is provided. The difference from the above-described Embodiment 1 is:

[0052]The second chip layer further includes: a plurality of conductive columns 400 'through the second insulating dielectric layer 210, each of which is electrically connected to the first interconnected structure layer 300, and the surface of the other end and the second insulating dielectric layer. 210 is parallel from the surface of the first interconnected layer 300.

[0053]The semiconductor package structure also includes a second interconnected layer 500 ', and the second interconnected structure layer 500' is located from the surface of the second chip layer away from the surface of the first interconnected structure layer 300, the second interconnected structure layer 500 'and a plurality of conductive columns 400 'Electrical connection;

[0054]The semiconductor package structure of the present embodiment, the second insulatin...

Embodiment 3

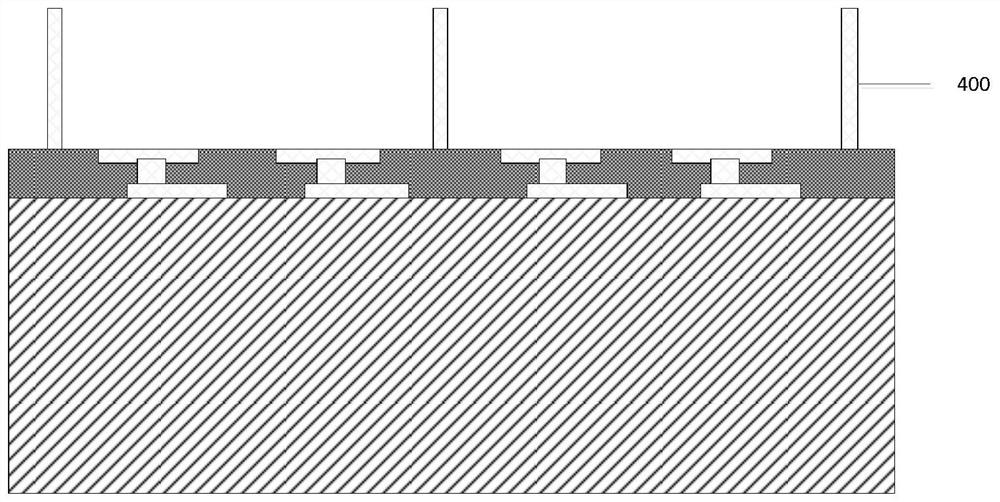

[0057]referenceFigure 1 - Figure 10 This embodiment provides a method of manufacturing a semiconductor package structure, including the following steps:

[0058]The first interconnected structure layer 300 is formed.

[0059]The first chip layer is formed, and the first chip layer is formed on one side surface of the first interconnected structure layer 300, and the first chip layer includes a plurality of first chip 100, and the first chip layer in the first chip layer is facing the first interconnection. The structural layer 300 is electrically connected to the first interconnected structure layer 300.

[0060]The second chip layer is formed, and the second chip layer is formed on one side surface of the first interconnected layer 300 to the first chip layer, and the second chip layer includes a plurality of second chip 200, the second chip 200 in the second chip layer 200. The front is electrically connected to the first interconnected structure layer 300 and is electrically connected to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com