Chip packaging structure, chip packaging method and electronic equipment

A chip packaging structure and chip packaging technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of difficult to guarantee communication quality, long physical distance, large attenuation of intermediate frequency signals, etc., to shorten physical distance and reduce signal attenuation. , reduce the effect of attenuation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0049] The chip packaging structure provided by the embodiments of the present invention can be used in various electronic devices involving millimeter wave transceivers, such as millimeter wave transceiver systems.

[0050] The specific structure of the chip packaging structure will be introduced below.

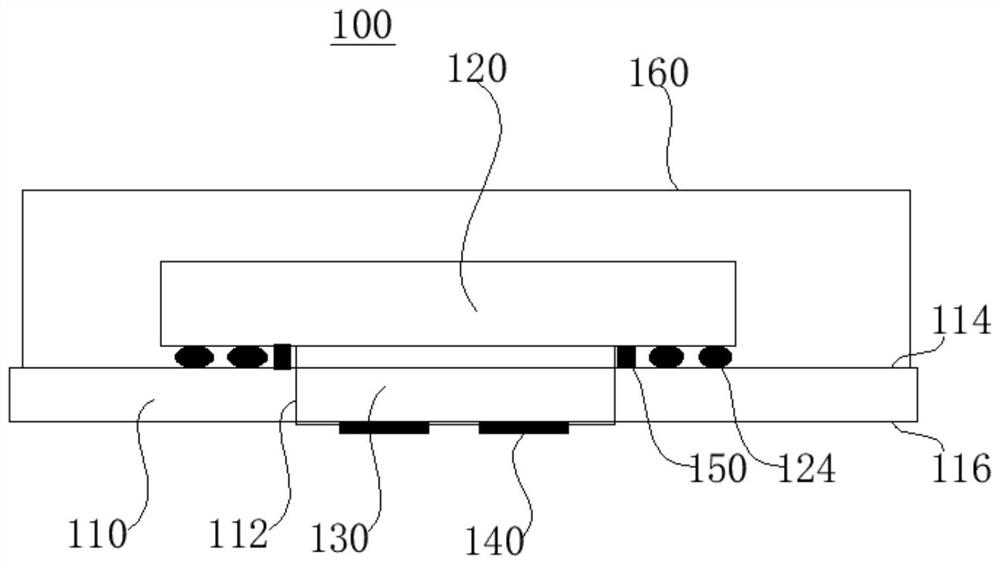

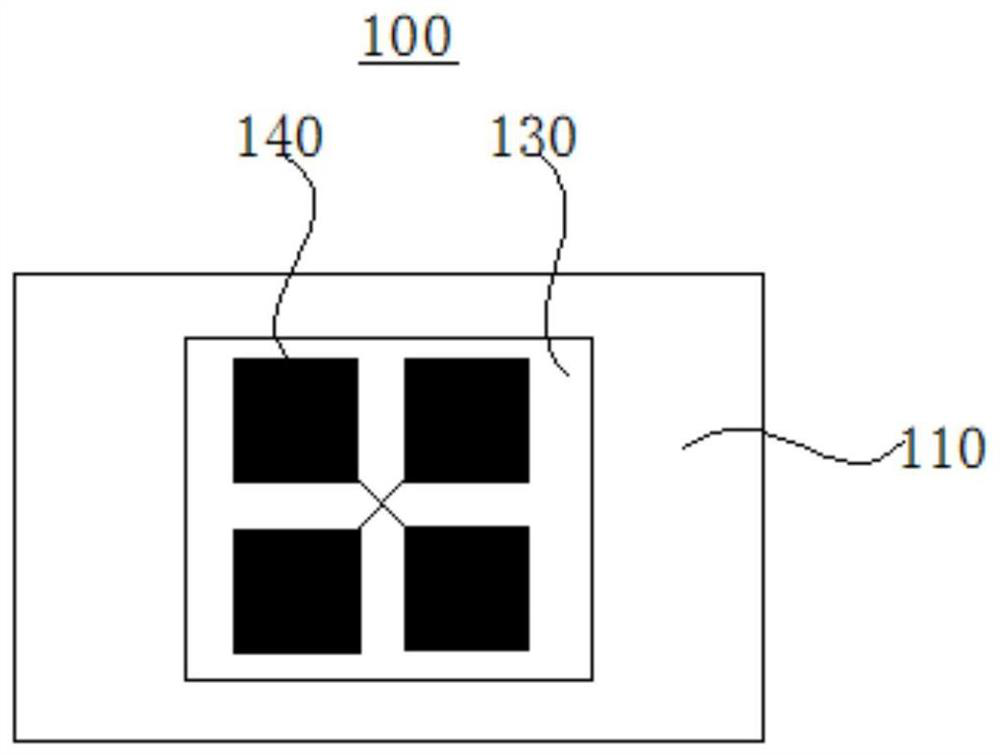

[0051] Please refer to figure 1 and figure 2 , the chip packaging structure 100 includes a substrate 110 , a first chip 120 , a second chip 130 and an antenna 140 . The first chip 120 is arranged on the substrate 110 and is electrically connected to the substrate 110, the second chip 130 is arranged on the first chip 120 and is electrically connected to the first chip 120, and the antenna 140 is arranged on the second chip 130 and is connected to the second chip. 130 electrical connection. The first chip 120 is used to output an intermediate frequency signal, the second chip 130 is used to process the intermediate frequency signal output by the first chip 120 to output a...

no. 2 example

[0076] Please refer to Figure 9 and Figure 10 , this embodiment also provides a chip packaging structure 100, its overall structure, working process and technical effects are basically the same as the chip packaging structure 100 provided in the first embodiment, the difference is that the substrate 110 and the second chip 130 relative positional relationship.

[0077] In this embodiment, the substrate 110 is no longer provided with the through hole 112, and the second chip 130 is arranged on the side of the first chip 120 away from the substrate 110. There is no need to set the shielding cover 160 on the top. Therefore, the chip packaging structure 100 provided by this embodiment has a simpler structure, and the corresponding manufacturing method is also simpler.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com