Inter-core communication method and device based on virtual data bus

A technology of inter-core communication and virtual data, which is applied in the field of inter-core communication of multi-core processors, can solve the problems of rapid inter-core deployment and inter-core communication of power secondary equipment at the same time, the inability of programs to flexibly respond to business changes, and application program design Increased difficulty and other issues to achieve the effect of avoiding tedious and repetitive inter-core communication development work, improving inter-core communication efficiency, and improving technology reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The application will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solutions of the present invention more clearly, but not to limit the protection scope of the present application.

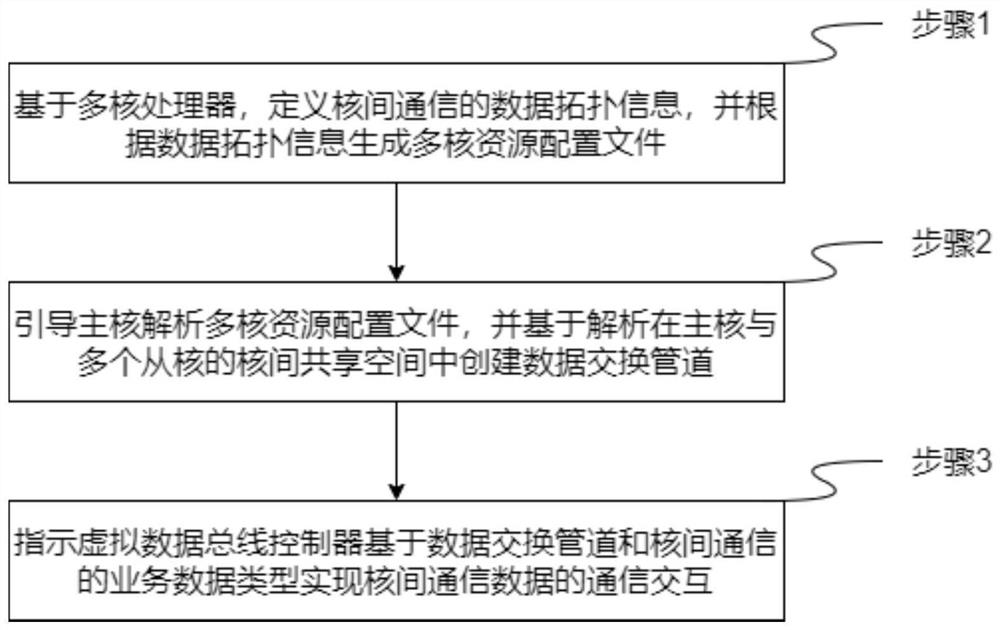

[0024] figure 1 It is a schematic flow chart of a virtual data bus-based inter-core communication method and device of the present invention. Such as figure 1 As shown, the first aspect of the present invention relates to an inter-core communication method based on a virtual data bus, including steps 1 to 3.

[0025] Step 1, based on the multi-core processor, define the data topology information of inter-core communication, and generate a multi-core resource configuration file according to the data topology information.

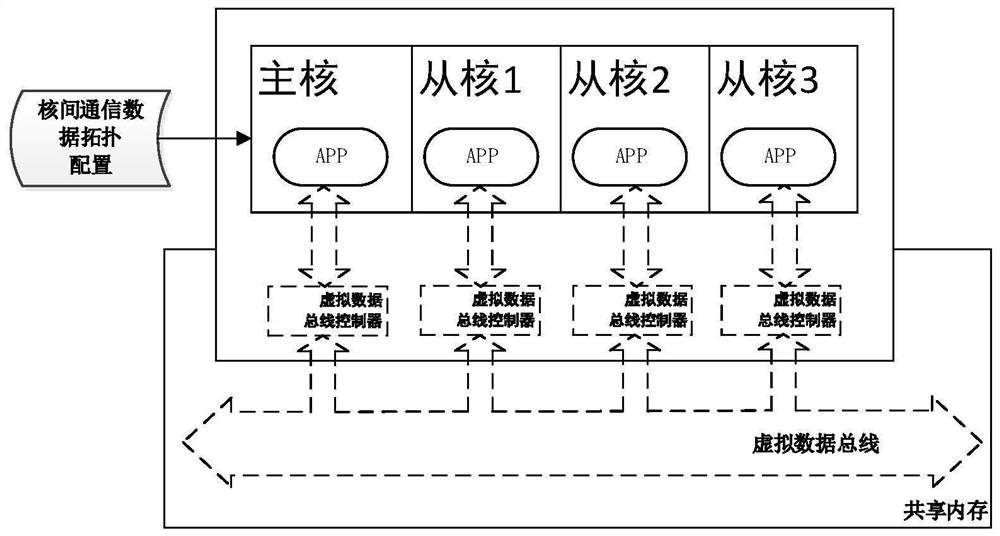

[0026] In an embodiment of the present invention, electric secondary equipment can be used, and multi-core processors can be used to run in AMP mode, and different application ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com