Novel SiC MOSFET oscillation suppression circuit applied to half-bridge circuit

A suppression circuit, half-bridge circuit technology, applied in circuits, high-efficiency power electronic conversion, electronic switches, etc., can solve the problems of complex distribution of power loop inductance, increased conduction loss of power devices, complex design, etc., and achieve simple structure and working principle , Reduce switching loss, suppress overvoltage effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention is described in further detail below in conjunction with accompanying drawing:

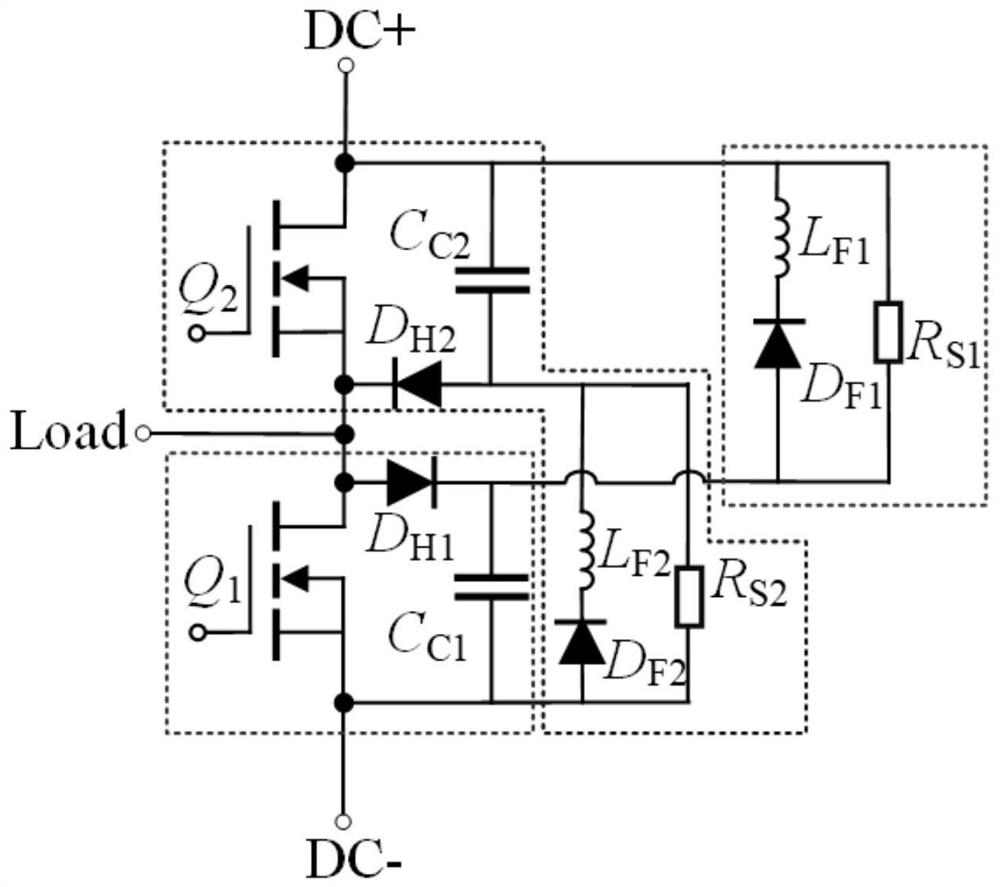

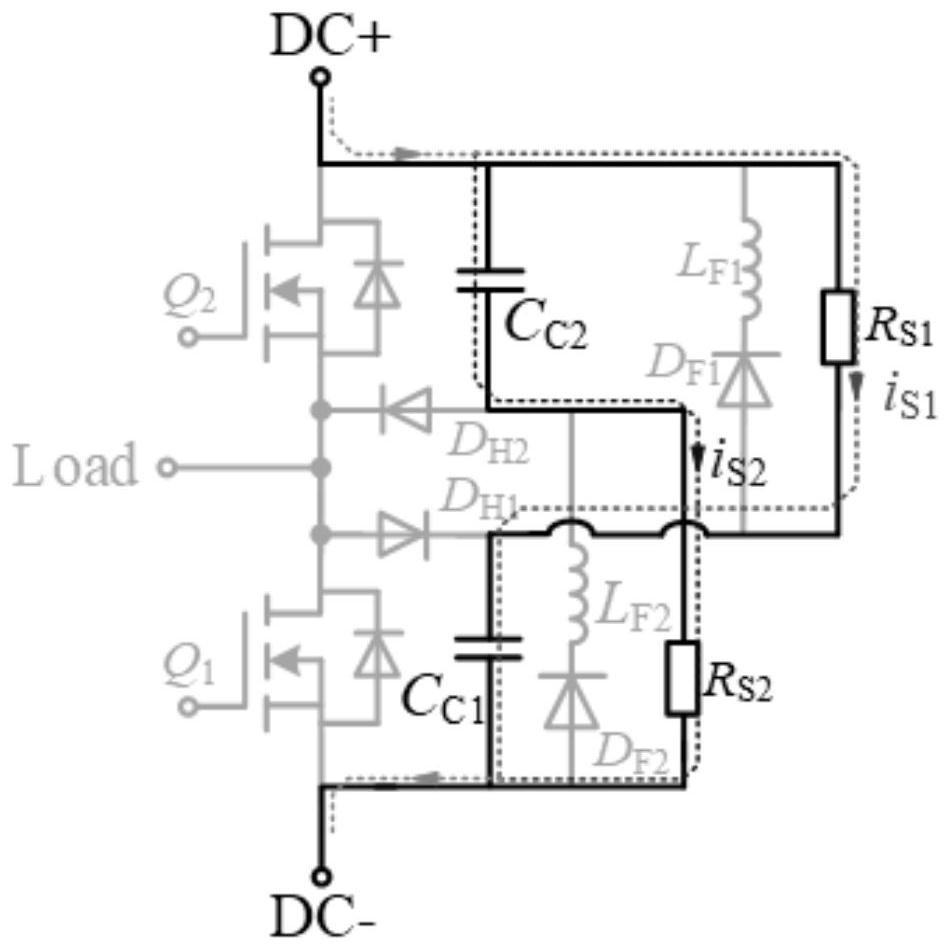

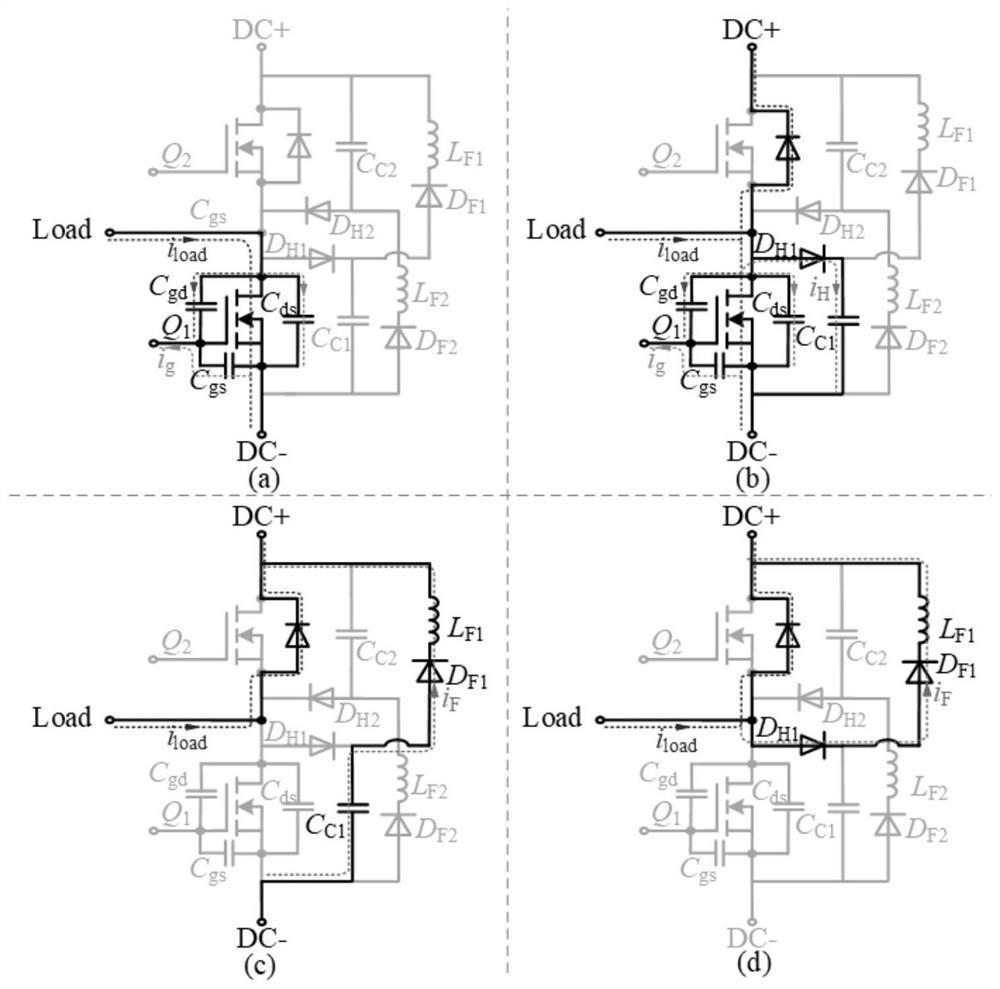

[0021] refer to figure 1 , the novel SiC MOSFET oscillation suppression circuit applied to the half-bridge circuit according to the present invention includes a DC bus, a first SiC MOSFET Q1, a second SiC MOSFET Q2, a first clamping capacitor C c1 , the second clamping capacitor C c2 , the first feedback module, the second feedback module, the load terminal, the first collecting diode D H1 , the second collection diode D H2 and low voltage source; the drain of the DC bus and the second SiC MOSFET tube Q2, and the second clamping capacitor C c2 One end of the first feedback module is connected to one end of the first feedback module, and the source of the second SiC MOSFET Q2 is connected to the second collection diode D H2 The negative pole, the load terminal, the first collector diode D H1 The anode and the drain of the first SiC MOSFET tube Q1 are connected, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com