Level shift circuit

A level shift circuit and circuit technology, which is applied in the connection/interface layout of logic circuits, coupling/interfaces of logic circuits using field effect transistors, etc., can solve the problem that the DRV_OUT signal cannot be output normally, the gate oxide of the MOS tube is broken down, and it is not easy to flip. and other problems, to achieve the effect of novel technical solution, accurate power consumption value, accurate power consumption control and

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

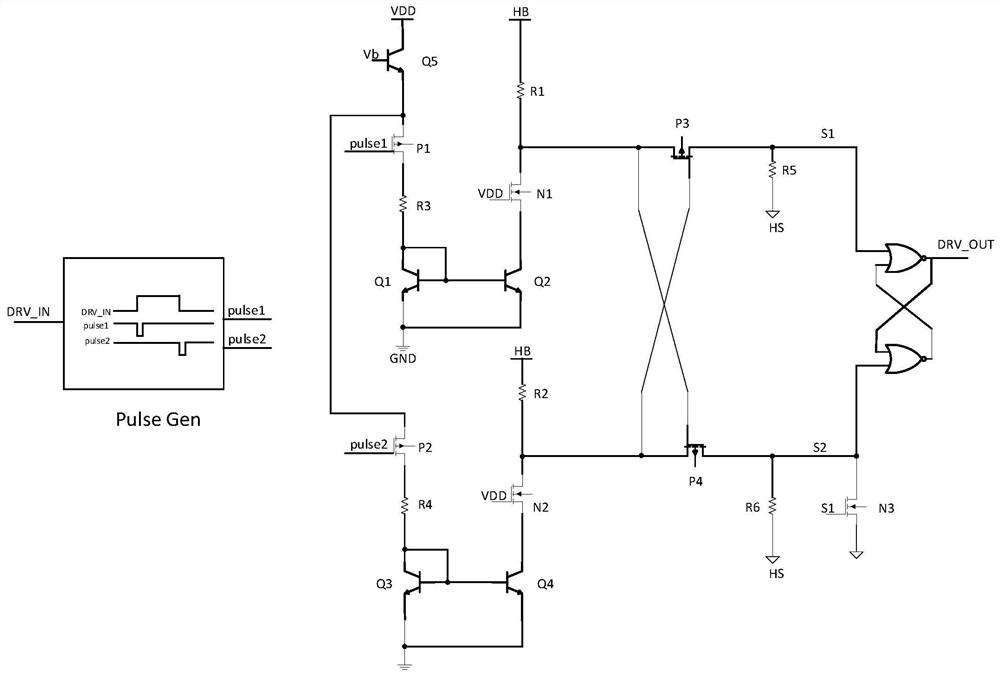

[0017] Embodiment 1: a level shift circuit, such as image 3 As shown, VDD is the chip power supply, usually 10-30V; GND is the chip ground; HB is the half-bridge high-side floating power supply, usually dozens of volts to hundreds of volts; HS is the half-bridge high-side floating ground; N1, N2 It is a MOS that withstands the high voltage of the half-bridge; R1 and R2 are two resistors that generate a voltage difference; Q1, Q2, Q3, and Q4 form two sets of current mirrors; Q5 is a current source that provides bias for the Q1 branch or Q3 branch respectively. The magnitude of the bias current is determined by the bias voltage Vb and the resistor R3 or R4; P1 and P2 are the switch tubes that control whether the two sets of current mirrors generate current, and are controlled by the pulse signal pulse1 and pulse2 respectively; P3 and P4 are the sampling The switch tube; R5, R6 resistors and N3 generate the initial state for the RS latch; the PulseGen module receives the DRV_IN ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com