Power module, chip embedded packaging module and preparation method

A packaging module, embedded technology, applied in the direction of printed circuit manufacturing, circuits, printed circuits, etc., can solve the problems of thermal expansion coefficient mismatch, chip edge position and delamination of insulating plastic packaging materials, etc., to achieve the effect of inhibiting delamination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

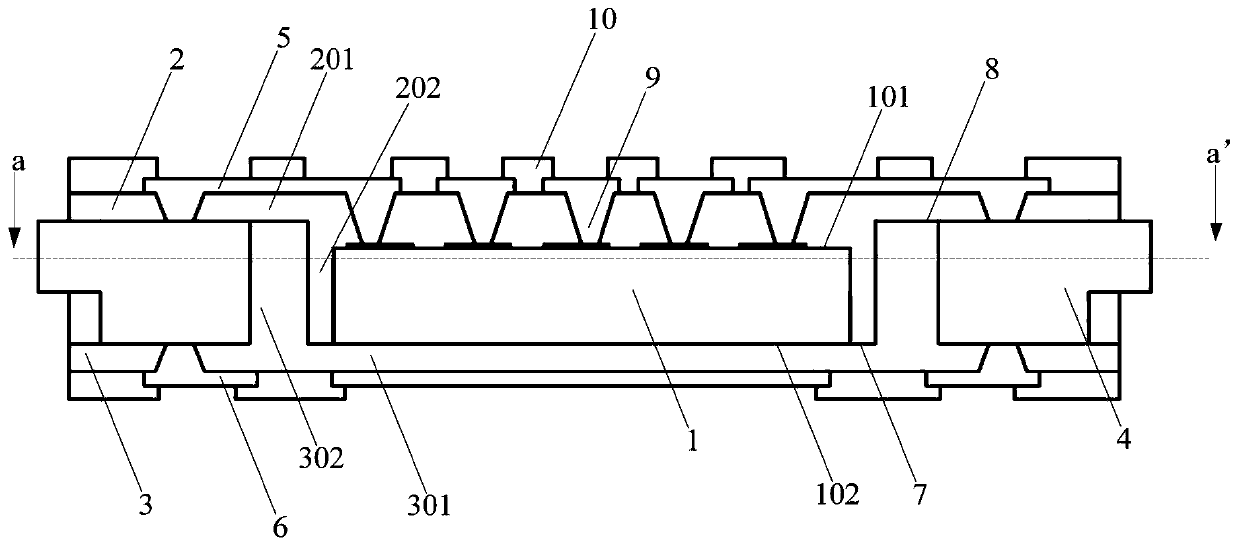

Image

Examples

Embodiment 10

[0133] The chip-embedded packaging module of the tenth embodiment shortens the circuit paths from the capacitor 14 to the input terminal of the module and the circuit paths to the two chips 1, and the effects of efficiency, current sharing and ripple cancellation can be further enhanced. If no capacitive parts are arranged above the packaging structure, the inductor 16 can be directly combined with the packaging structure, and the structure can be more compact. Other capacitors may also be provided outside the chip 1, and these capacitors may be input capacitors Cin, output capacitors Co, and so on. The current sharing effect and ripple cancellation effect of this structure are further enhanced when the two-phase half-bridge circuit is connected in parallel, which is beneficial to reduce the number of capacitors or the demand for capacitance value, the structure is more compact, and the heat dissipation effect is better.

[0134] It can be seen from the above embodiments that ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com