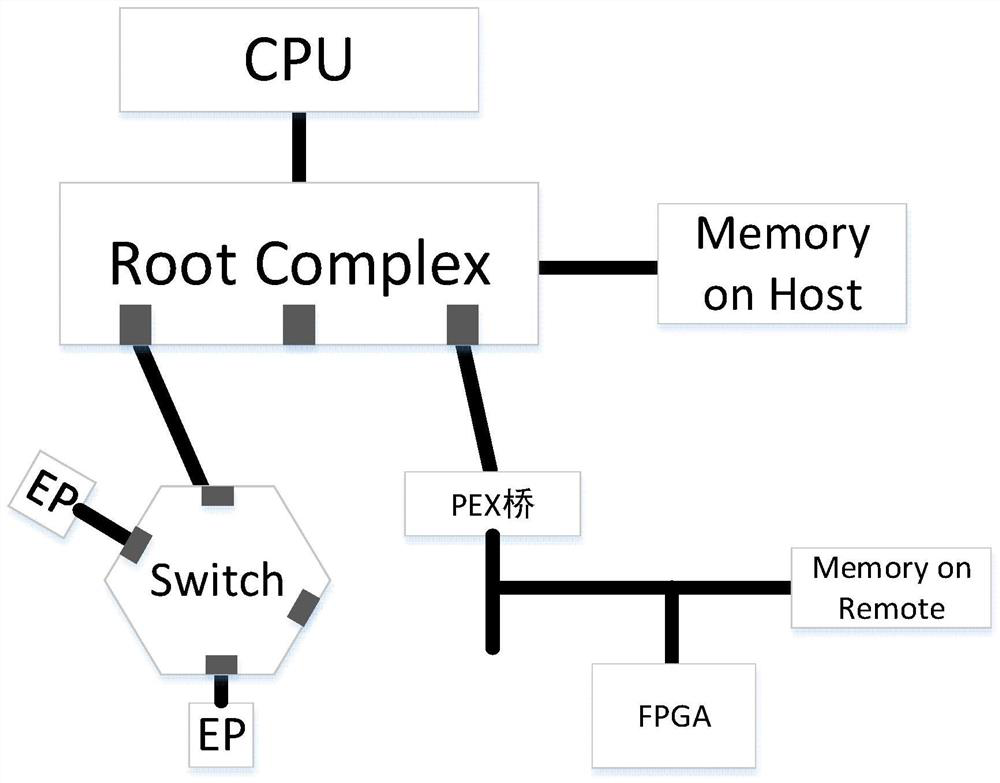

A data synchronization method between the host end and fpga accelerator

A data synchronization, host-side technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

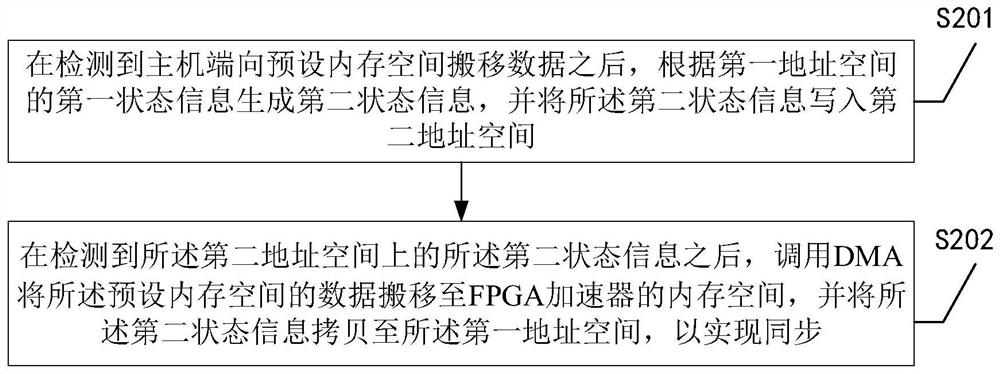

[0037] Embodiment 1 of a data synchronization method between a host end and an FPGA accelerator provided by the present application is introduced below, see figure 2 , embodiment one includes:

[0038] S201. After detecting that the host moves data to the preset memory space, generate second state information according to the first state information in the first address space, and write the second state information into the second address space;

[0039] Wherein, the first address space and the second address space are different address spaces mapped on the host side by the Bar space, the first state information includes the last data frame number and the current data frame number, and the second The two-state information includes the current data frame number and the next data frame number.

[0040] S202. After detecting the second state information on the second address space, call DMA to move the data in the preset memory space to the memory space of the FPGA accelerator,...

Embodiment 2

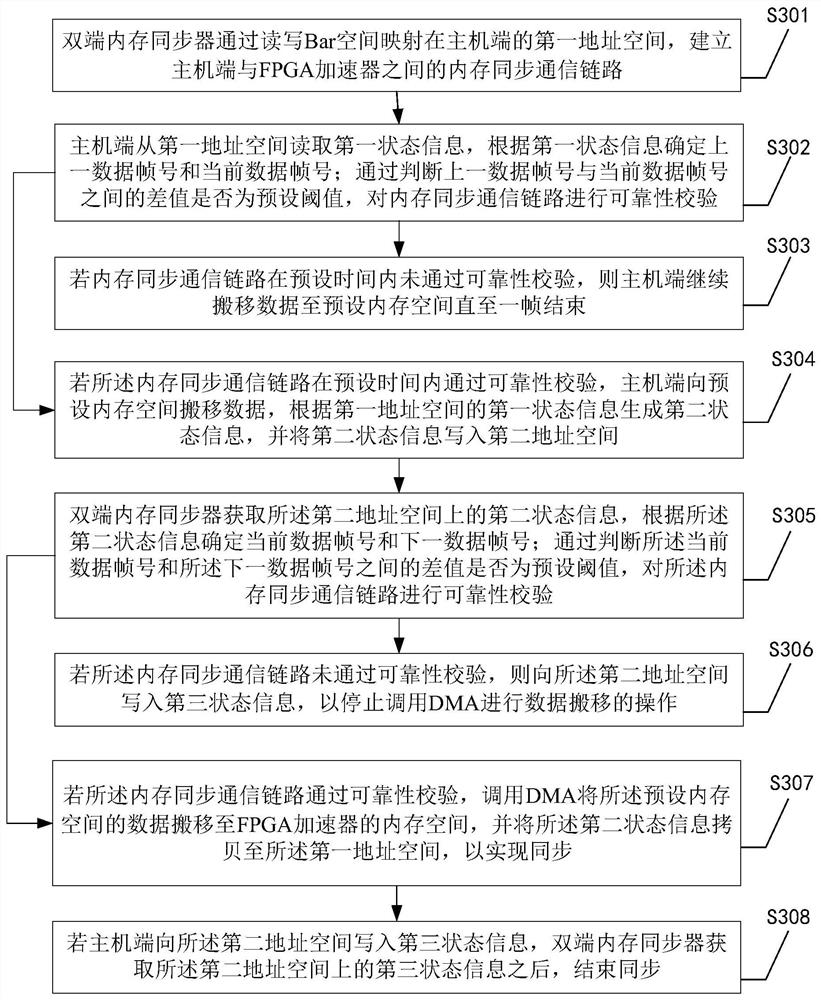

[0048] see image 3 , embodiment two specifically includes:

[0049] S301. The dual-terminal memory synchronizer maps the first address space on the host side by reading and writing the Bar space, and establishes a memory synchronization communication link between the host side and the FPGA accelerator;

[0050] S302. The host terminal reads the first state information from the first address space, and determines the last data frame number and the current data frame number according to the first state information; by judging the difference between the last data frame number and the current data frame number Whether it is a preset threshold, and check the reliability of the memory synchronization communication link;

[0051] S303. If the memory synchronous communication link fails the reliability check within the preset time, the host continues to move data to the preset memory space until the end of one frame;

[0052] S304. If the memory synchronous communication link passe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com