Ultralow-loss low-end ideal diode

An ideal diode, ultra-low technology, used in data processing power supply, electrical digital data processing, digital data processing components and other directions, can solve the problems of large on-resistance, large current loss, high cost, simple circuit, prevent backflow , cheap effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The embodiments of the present invention will be described in detail below with reference to the accompanying drawings, but the present invention can be implemented in many different ways defined and covered by the claims.

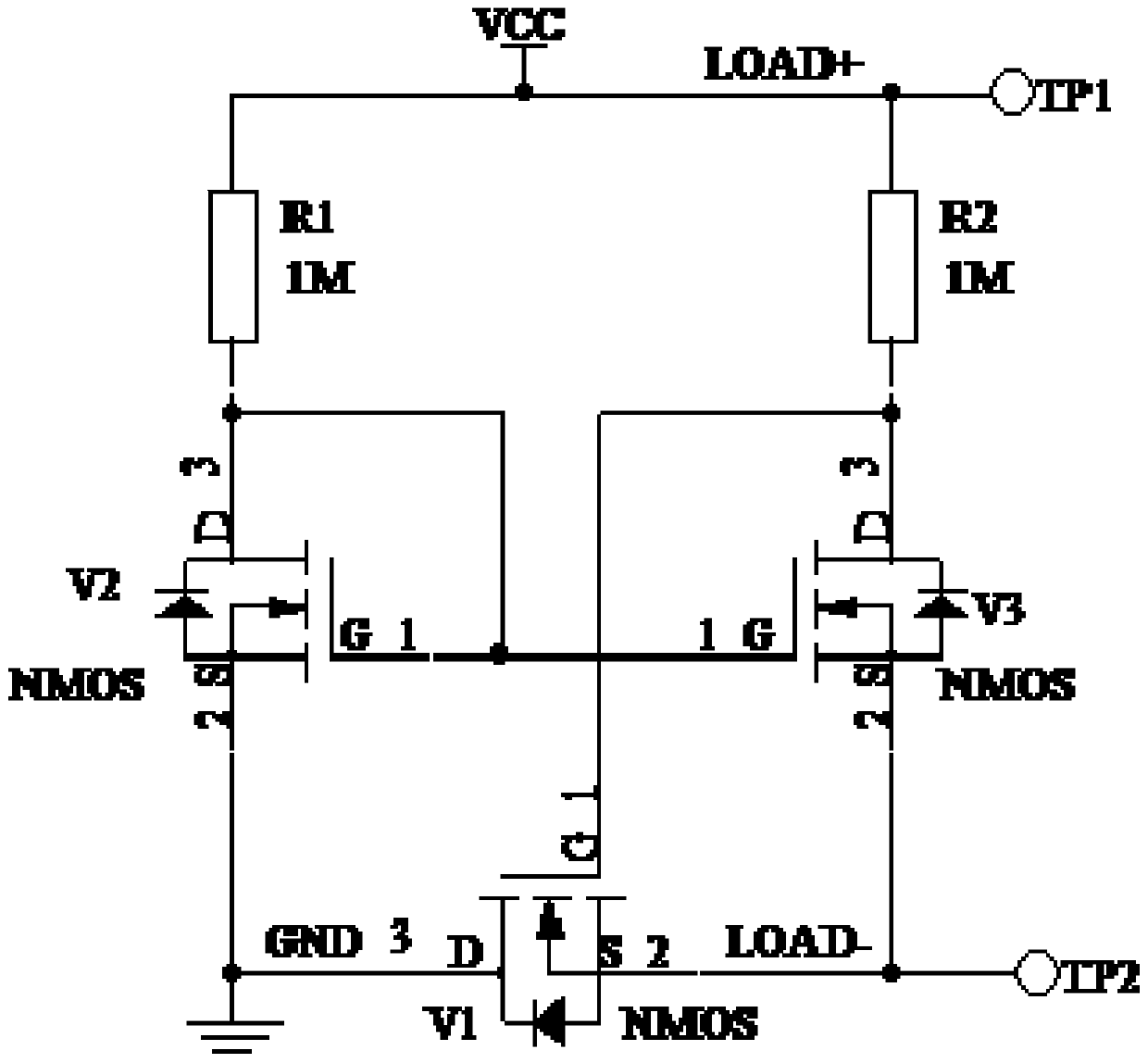

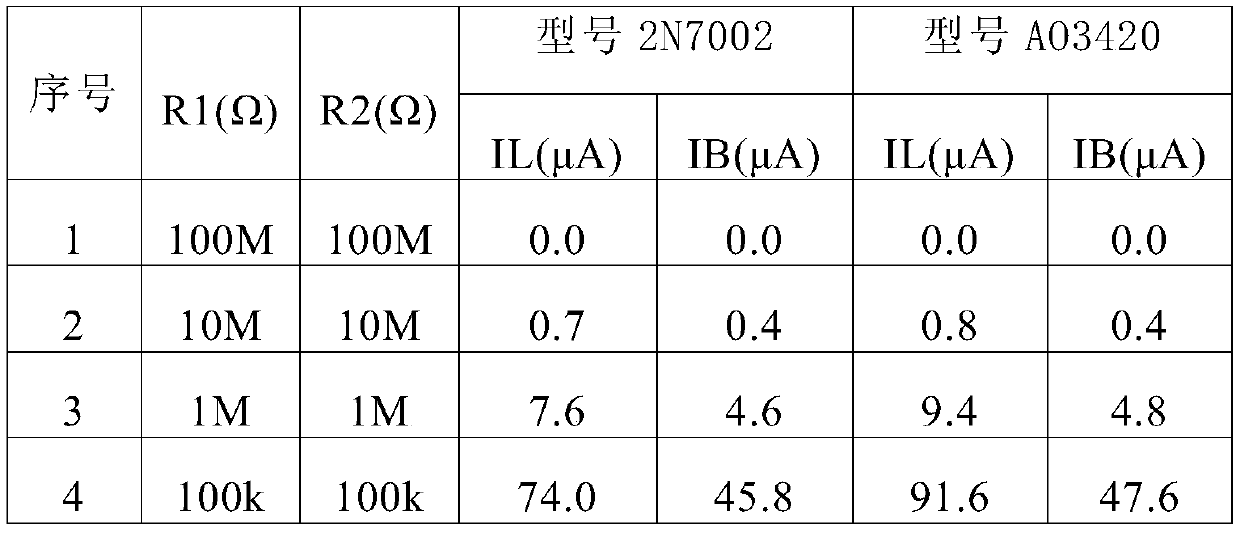

[0028] Such as figure 1As shown, the combinational logic control circuit is composed of two NMOS transistors (V2, V3) of the same type or NMOS pair transistors with the same parameters packaged together, and two serial resistors (R1, R2) to control the NMOS transistors ( V1) conduction and cut-off: when the voltage LOAD- is not less than the voltage GND, the NMOS transistor (V1) is turned on; otherwise, the NMOS transistor (V1) is cut off, preventing the GND current from flowing backward through the NMOS transistor (V1) to LOAD-, protecting LOAD - load circuit. Since the NMOS tube is a voltage device, the current of the NMOS tube is very small when it is turned on and off, and the large resistance resistor connected in series can be ignored. Compa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com