Efficient memory access address bit flipping statistical device

A technology for accessing memory addresses and memory, which is applied in the field of high-efficiency memory address bit flip statistics devices, which can solve problems such as incompleteness and inaccuracy, and achieve the effects of convenient operation, simple device structure, and simple implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

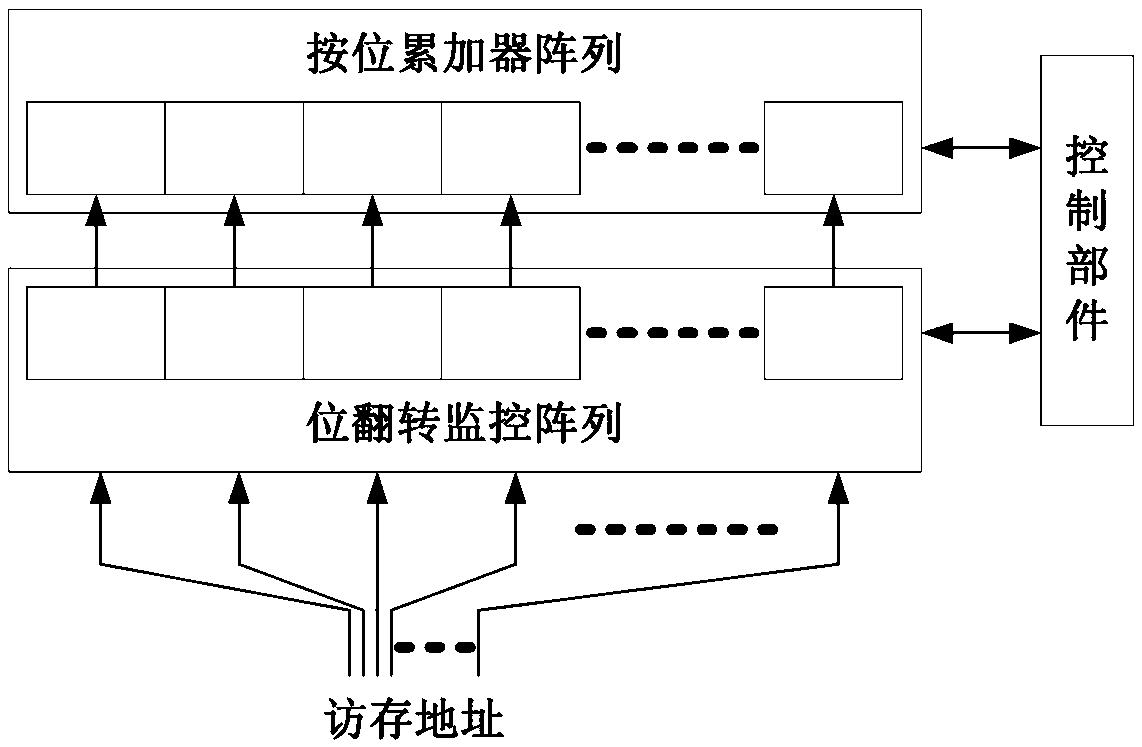

[0024] Such as figure 1 As shown, the memory access address bit flip statistics device of this embodiment includes:

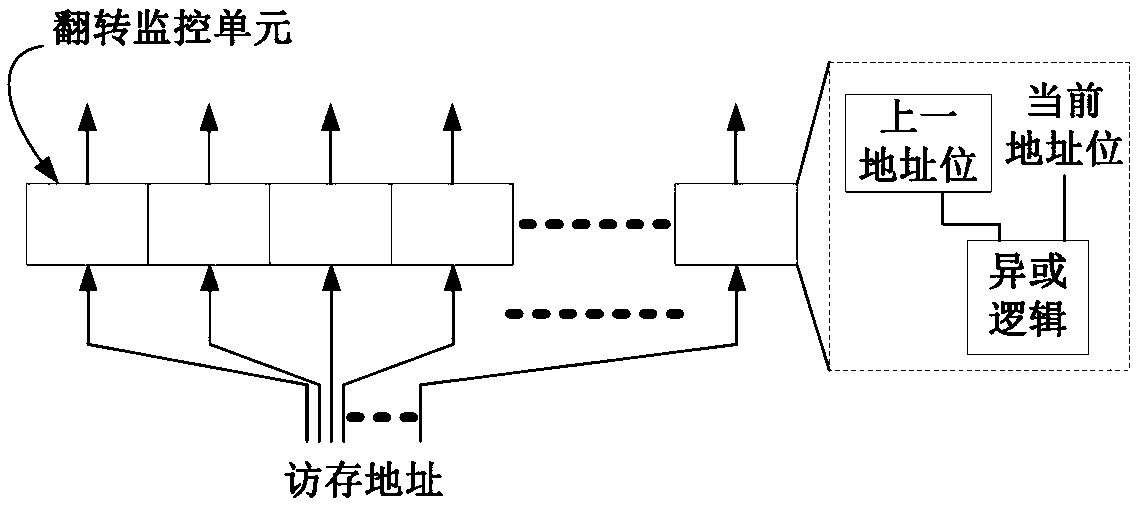

[0025] The bit flip monitoring array is mounted on the storage bus of the high-bandwidth memory, and is used to trigger the access count of the corresponding storage channel according to each effective access of the storage channel;

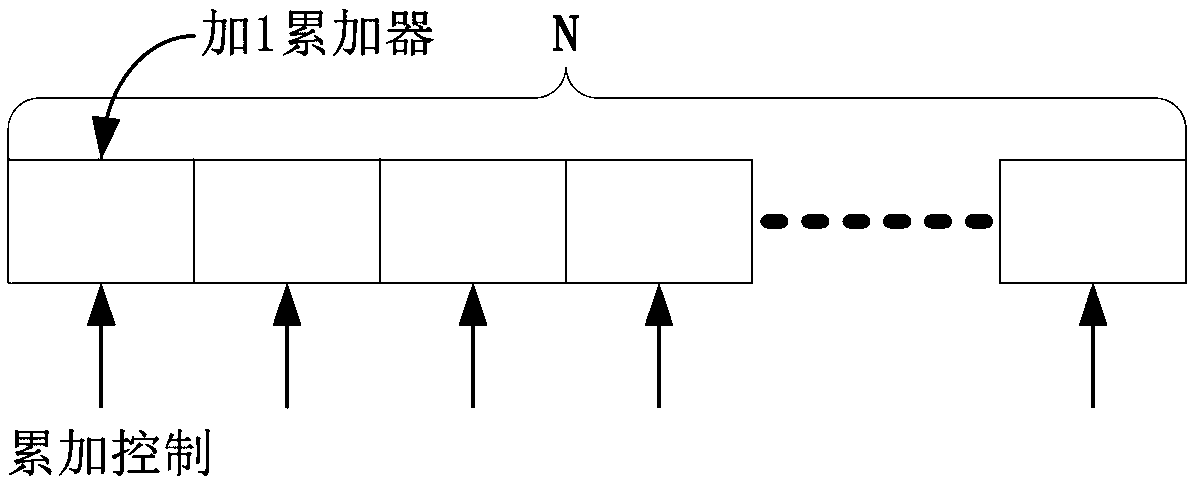

[0026] A bitwise accumulator array, used to record the access count of each storage channel;

[0027] The control part is used for enabling and resetting the storage channel access statistics module and providing an external access count reading operation.

[0028] from figure 1 It can be seen from the figure that the memory access address bit inversion statistics device in this embodiment is composed of a bitwise accumulator array, a bit inversion monitoring array and a control unit. The bit flip monitoring array is directly connected to the memory access address bus, and is used to monitor whether each bit address flips, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com