A room temperature terahertz focal plane array bias voltage adjustment circuit and its application method

A terahertz coke, planar array technology, applied in the field of room temperature terahertz detection, can solve the problems of low precision and difficult debugging, and achieve the effect of strong flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

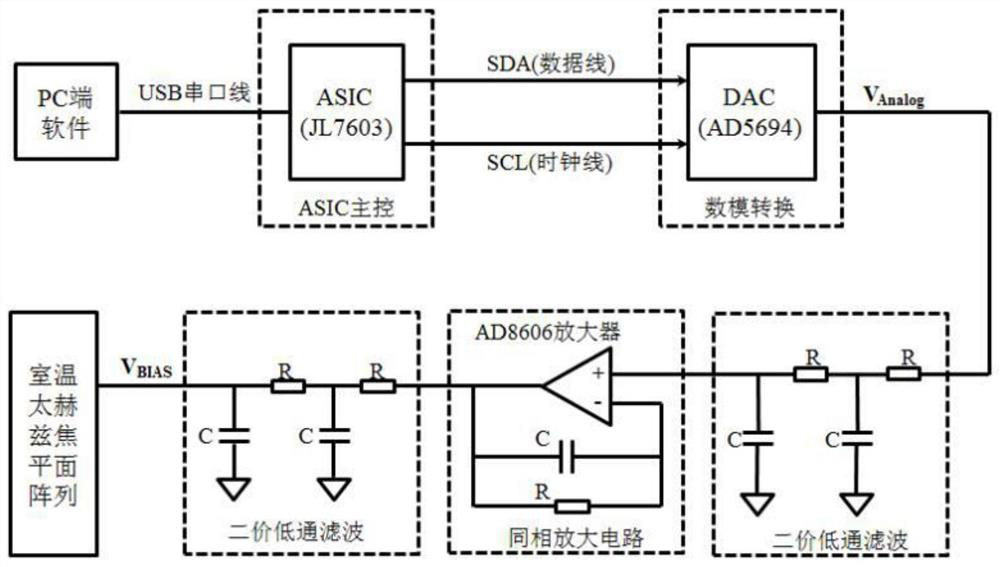

[0037] Taking the ASIC chip JL7603B, the 14-bit D / A converter AD5694 and the 320*240 room temperature terahertz focal plane array detector as examples, a room temperature terahertz focal plane array bias voltage adjustment circuit is described in detail.

[0038] Such as image 3 As shown, the bias voltage adjustment circuit includes sequentially connected PC terminal, ASIC chip, D / A converter, first second-order low-pass filter, non-inverting amplifier circuit, second second-order low-pass filter and room temperature terahertz Focal plane array; the PC end is connected to the ASIC chip through a USB serial port, and the ASIC chip communicates with the PC end by converting the UART to a USB serial port. The SDA pin and the SCL pin of the ASIC chip are connected to the input end of the D / A converter through the SDA data line and the SCL data line. The ASIC chip processes the bias voltage value input from the PC terminal into a corresponding binary value through internal code, ...

Embodiment 2

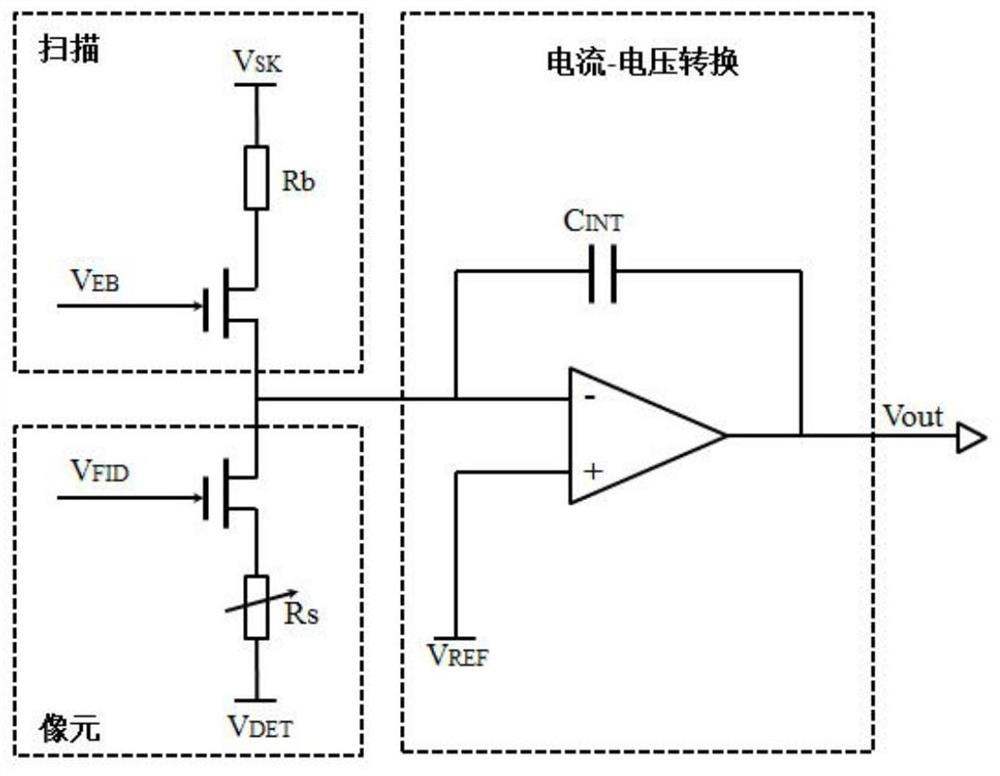

[0059] Such as figure 1 As shown, the room temperature terahertz focal plane array includes a pixel integration circuit based on a terahertz microbolometer, and there are four bias voltages VSK, VEB, VFID and VREF, and the range is between 0-5V. VSK provides the bias voltage for the blind resistor, VEB and VFID respectively control the current of the blind resistor and the equivalent resistance of the terahertz microbolometer, VREF is the reference voltage of the integrator, and the four bias voltages are crucial to the output voltage Vout Different bias voltage drivers will get different output voltage values, so the bias voltage needs to be designed to be adjustable.

[0060] Such as Figure 4 As shown, a method for using a room temperature terahertz focal plane array bias voltage adjustment circuit is provided, including the following steps:

[0061] S1. Input a bias voltage command in the PC-side software, and calculate the decimal value corresponding to the bias voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com