Multi-CPU brain-like simulation system

A technology for simulating systems and computing nodes, applied in the computer field, can solve problems such as high power consumption, large size, and low efficiency, and achieve the effects of reducing traversal time, reducing the number of table items, and improving scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

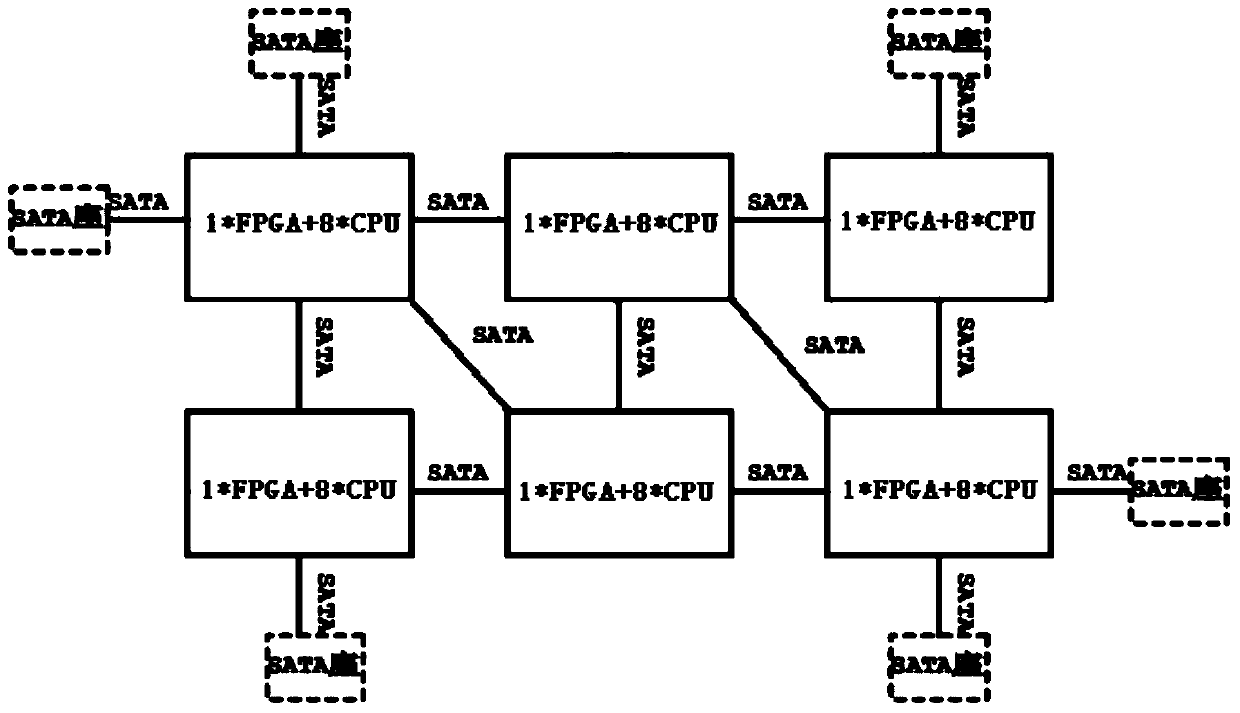

[0041] Such as figure 1 As shown, a kind of multi-CPU brain-inspired simulation system described in this embodiment includes a plurality of brain-inspired simulation system motherboards 1, and the multiple brain-inspired simulation system motherboards 1 are connected in an orderly manner; the brain-inspired simulation system motherboard 1 is composed of six Computing nodes 2 are composed of computing nodes 1, 2, 3, 4, 5, and 6 respectively. Computing nodes 2 and brain-inspired simulation system motherboard 1 communicate through SATA interfaces, such as figure 2 shown.

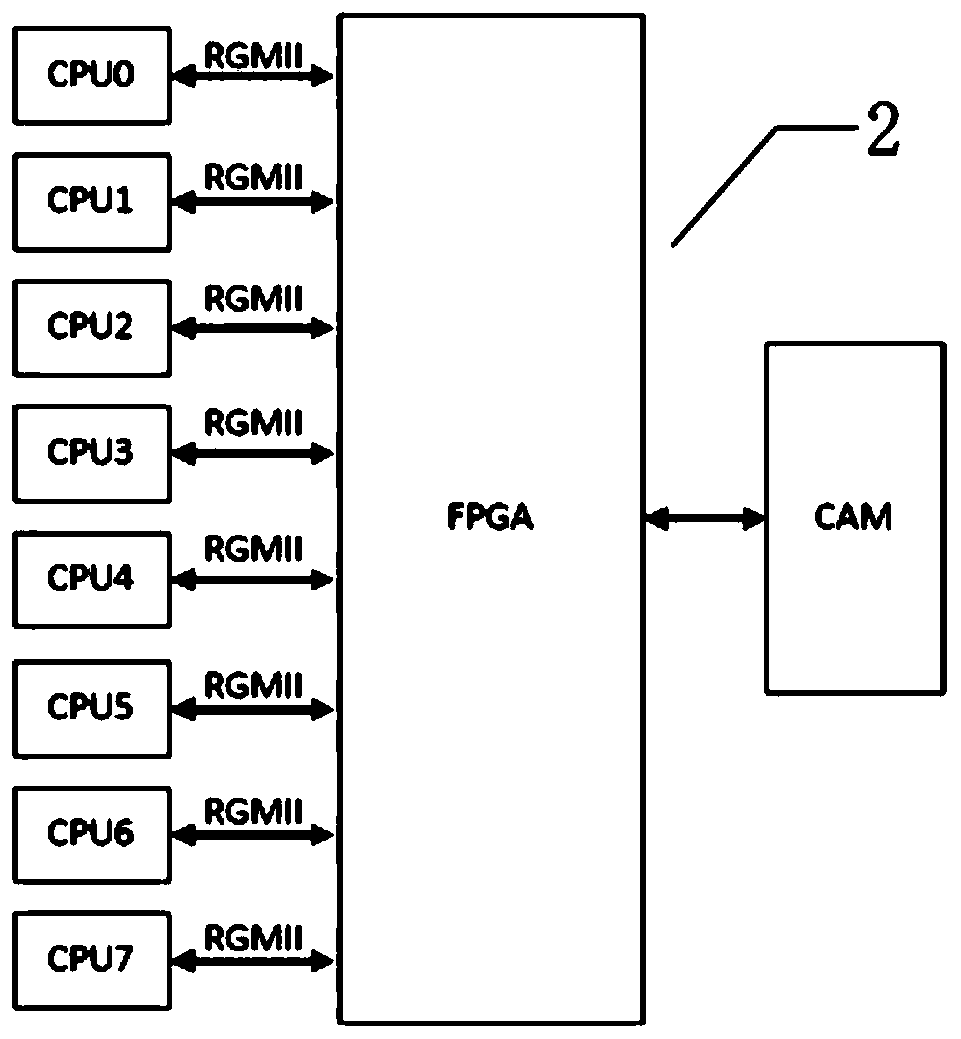

[0042] Such as image 3 As shown, the computing node 2 includes eight CPUs and a routing system; the routing system is composed of FPGA and CAM, and the CPU and FGPA are connected by an RGMII communication interface.

[0043] Due to the huge number of connections between the nodes of the multi-CPU brain-like simulation system, it is necessary to have symmetry to realize the connection between the circuit boa...

Embodiment 2

[0052] Compared with Embodiment 1, the present embodiment 2, CPU is multi-core CPU, adopts single CPU multi-core analog neuron, specifically as follows:

[0053] Single CPU multi-core simulates neurons, that is, uses multiple threads to work together to simulate neurons. To realize single CPU multi-core analog neuron, two key problems need to be solved: the problem of sending data packets to other threads and the problem of addressing received pulse data packets.

[0054] In order to solve these two problems, a routing thread for processing the routing of pulse data packets between neuron threads is bound on one core of the multi-core CPU, a clock synchronization thread is bound on one core, and all other cores are bound There are threads for simulating neurons, an internal buffer for storing pulse data packets generated by neurons in the thread, and a receiving buffer for storing pulse data packets sent by other threads; and the multi-core CPU is provided for sending outside ...

Embodiment 3

[0059] Combined with the hardware platform of the multi-CPU brain-like simulation system, the single-CPU multi-core analog neuron system is further optimized to realize multi-CPU multi-core analog neuron.

[0060] Compared with Embodiment 2, this embodiment 3 has an external receiving cache for receiving the pulse data packets sent by the routing system, and at the same time increases the network service function based on the original socket for receiving / sending data into the routing system, such as Figure 9 shown. And add an outgoing flag bit in the forwarding flag variable of the neuron, when this bit is 1, it means sending the pulse data packet outside the CPU.

[0061] The forwarding process of the pulse data packet from the thread to the routing thread is the same as that of a single CPU multi-core analog neuron. The difference is that when judging the flag variable, it is necessary to judge whether the outgoing flag is 1, and if it is 1, the pulse data will be forwar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com