A memory testing device and system

A memory test and memory technology, applied in the field of memory, can solve the problem of low test efficiency and achieve the effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0030] As mentioned in the background art, the existing memory generally needs to be tested after production. For example, OTP (One Time Programmable, one-time programmable) memory, generally speaking, the tests that the integrated OTP chip needs to do during the machine test stage include:

[0031] 1. Blank Check Test, the purpose of this test is to detect whether the chip storage space is all zero, if it is detected that the storage space is all zero, then the chip should be classified as a good chip; if it is detected as 1 bits, then this chip should be classified as scrap.

[0032] 2. Word Line and Bit Line Integrity Test (Word Line and Bit Line Integrity Test), the purpose of this test is to detect the integrity of the word line and bit line in the OTP storage space and whether the corresponding peripheral circuits have serious defects.

[0033] 3. Pre-program Test (Pre-program Test), the purpose of this test is to screen out chips with serious defects in the programming...

no. 2 example

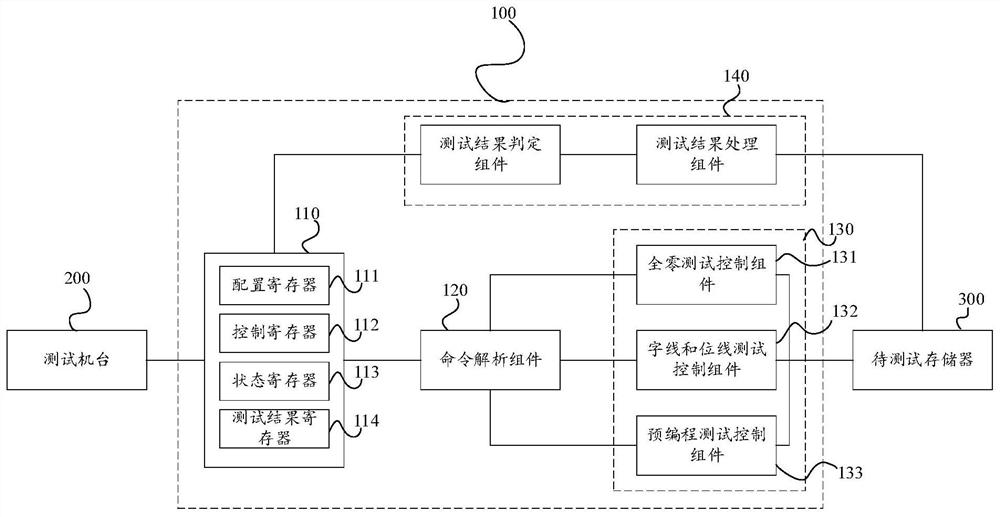

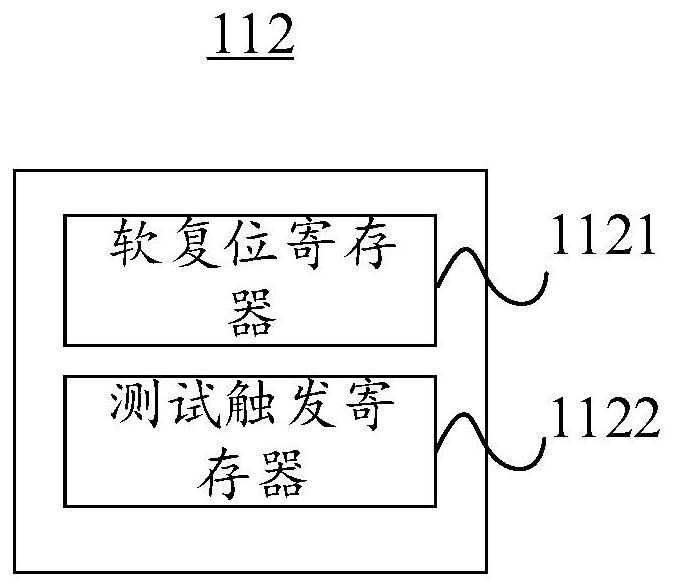

[0068] see figure 1 and figure 2 , the embodiment of the present invention also provides a memory test system, the memory test system includes a test machine 200, a memory 300 to be tested and the memory test device 100 described in the first embodiment, the test machine 200, the memory test device 100 And the memory 300 to be tested is connected in sequence, and the testing machine 200 is used to test the memory 300 to be tested by the memory testing device 100 . Since the first embodiment has described the hardware of the memory testing device 100 and the corresponding working principle in detail, so this embodiment will not repeat it here.

[0069] In summary, the present invention provides a memory testing device and system. The memory testing system also includes a test machine and a memory to be tested. The memory testing device includes a register component, a command analysis component, a test control component, a test result acquisition component, and a register com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com