A Method of Execution of Vector Storage Instruction with Abnormal Return

A technology of storing instructions and returning with exceptions, which is applied in the direction of machine execution devices, register devices, instruments, etc., can solve the problems of not being able to make full use of the memory access parallelism of the storage system, increasing the complexity of implementation, wasting hardware resources, and returning with exceptions. No public information and other issues to achieve the effect of reducing the implementation cost, reducing the number of channels, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

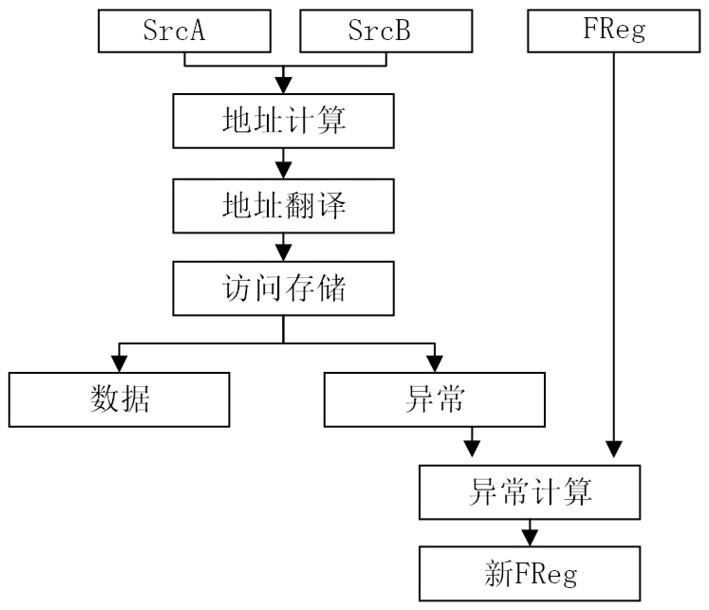

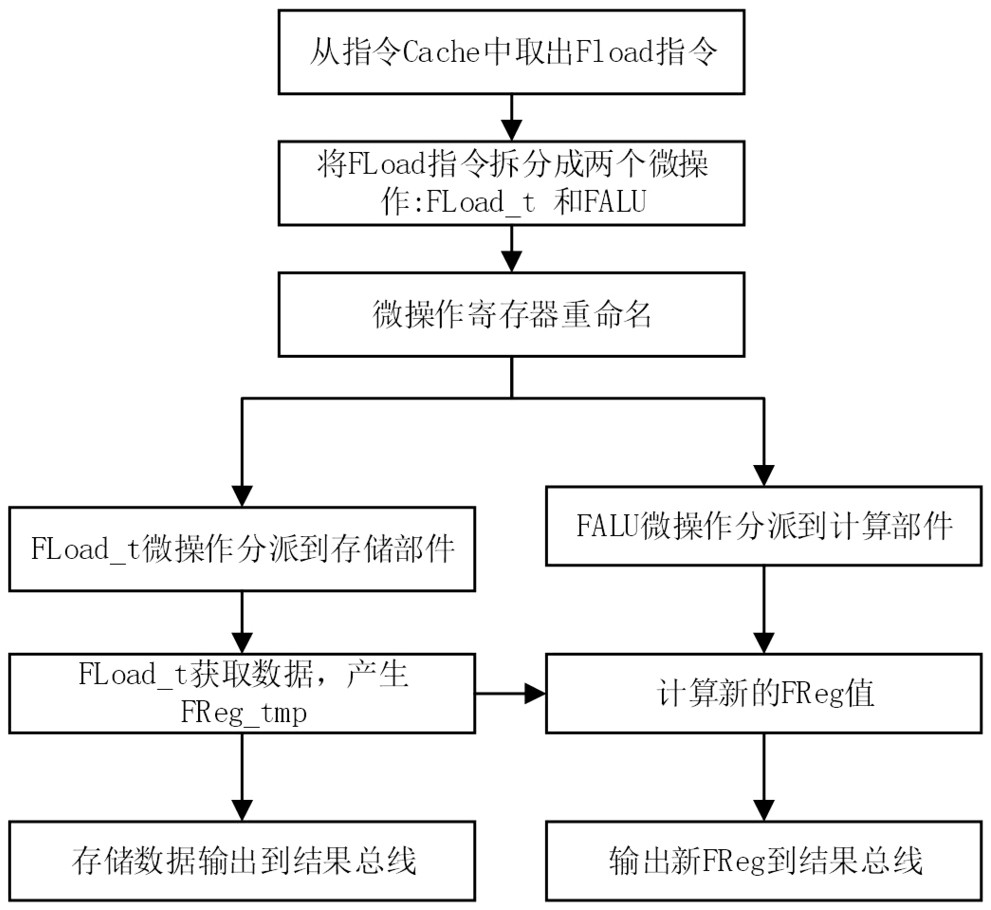

[0037] Such as image 3 and Figure 4 As shown, the implementation steps of the execution method of the vector storage instruction with abnormal return in this embodiment include:

[0038] 1) The vector storage instruction FLoad with exception return is fetched from the instruction buffer, and this process is the same as the prior art realized by the microprocessor.

[0039] 2) Split the vector storage instruction FLoad with exception return into two micro-operations, the first micro-operation is the storage operation FLoad_t, and the second micro-operation is the exception information calculation operation FALU;

[0040] 3) Parse operand information in units of micro-operations;

[0041] The first micro-operation FLoad_t split from the vector storage instruction FLoad needs to be decoded to find out that the micro-operation has two source registers and two destination registers. For the second micro-operation FALU, decoding needs to resolve that the micro-operation has two...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com