Three-dimensional memory structure and preparation method thereof

A memory, three-dimensional technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problem of increasing gate word line resistance, achieve the effects of reducing resistance, improving device performance, and relieving stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

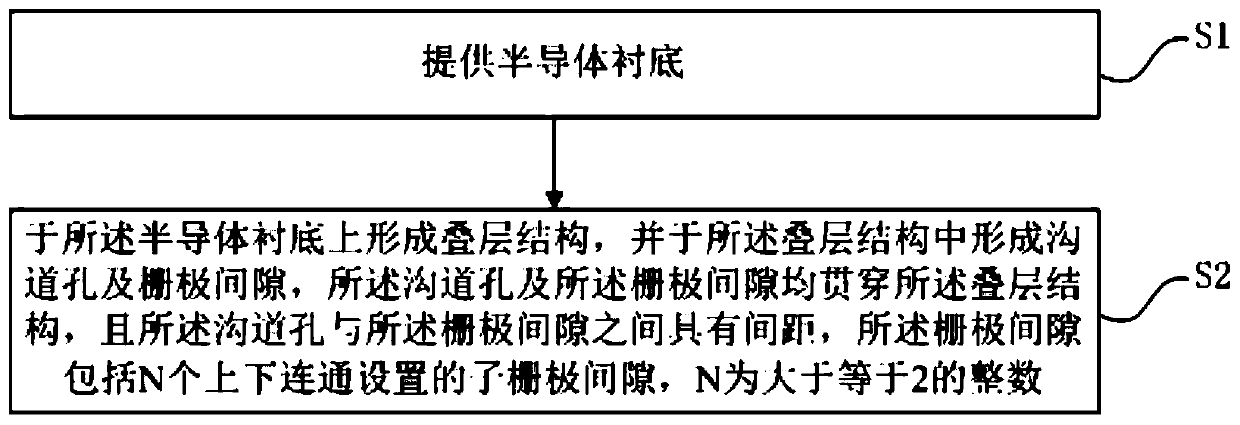

[0107] Such as figure 1 As shown, the present invention provides a method for preparing a three-dimensional memory structure, comprising the following steps:

[0108] Provide semiconductor substrates;

[0109] forming a stacked structure on the semiconductor substrate, and forming a channel hole and a gate spacer in the stacked structure, the channel hole and the gate spacer both passing through the stacked structure, In addition, there is a distance between the channel hole and the gate spacer, and the gate spacer includes N sub-gate spacers connected up and down, where N is an integer greater than or equal to 2.

[0110] The preparation process of the three-dimensional memory structure in the present invention will be described in detail below in conjunction with the accompanying drawings.

[0111] Such as figure 1 S1 and figure 2 As shown, a semiconductor substrate is provided.

[0112] Specifically, the semiconductor substrate 101 can be selected according to the act...

Embodiment 2

[0168] Such as Figure 22 and Figure 23 shown, refer to Figure 1-21 , the present invention also provides a three-dimensional memory structure, the three-dimensional memory structure is preferably prepared by the preparation method of the present invention, the three-dimensional memory structure includes:

[0169] semiconductor substrate 101; and

[0170] The stack structure 118 is formed on the semiconductor substrate 101, the channel hole 106 and the gate spacer 107 are formed in the stack structure 118, and the stack structure 118 includes alternately stacked gate layers and insulating dielectric layers 103, the channel hole 106 and the gate spacer 107 both pass through the stacked structure 118, and there is a distance between the channel hole 106 and the gate spacer 107, and the gate spacer 107 includes N sub-gate isolation grooves 107a connected up and down, where N is an integer greater than or equal to 2.

[0171] Specifically, the semiconductor substrate 101 can...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com