Packaging structure for system heat dissipation and packaging process

A technology of packaging structure and packaging process, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of too large heat flow density and too small heat dissipation path of packaging chips that cannot be improved, and achieve improved heat transfer performance. , Improve heat dissipation performance, good heat dissipation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

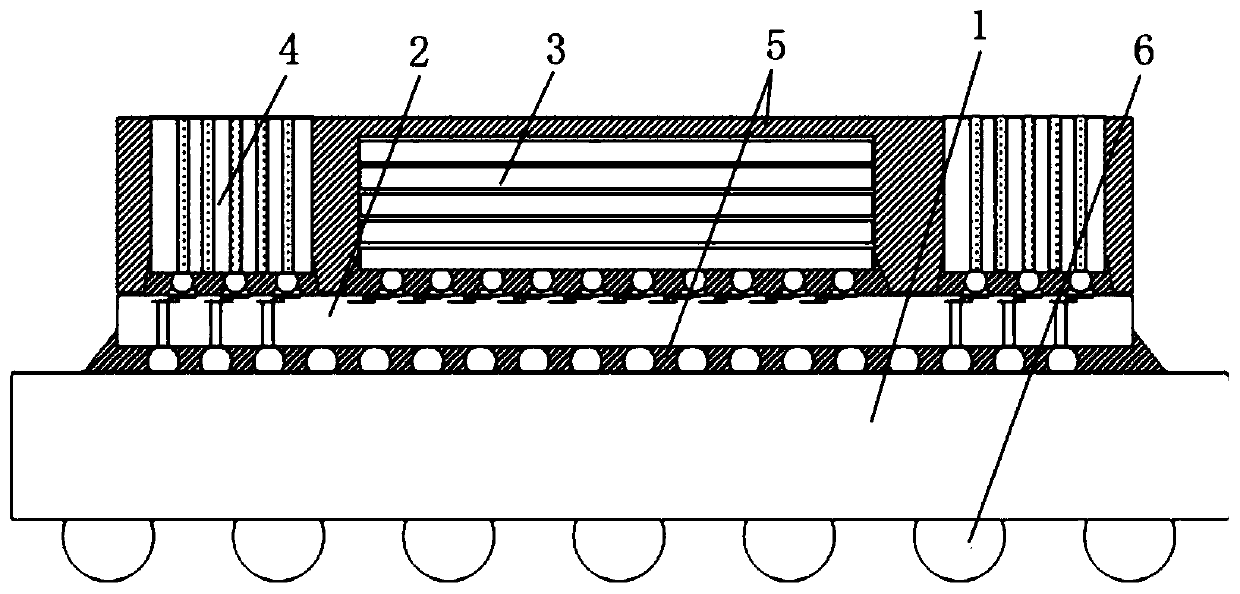

[0042] A package structure for system heat dissipation, such asfigure 1 As shown, it includes: a substrate 1, an active chip 2, a memory chip 3, a heat conductor 4 and a package body 5; wherein, the active chip 2 is mounted on the substrate 1; the memory chip 3 is mounted on the active chip 2; The heat conductor 4 and the memory chip 3 are mounted on the same surface of the active chip 2, and the heat conductor 4 has a second TSV interconnected with the active chip 2; the package body 5 integrates the active chip 2, The memory chip 3 and the heat conductor 4 are packaged on the substrate 1 , one end of the second TSV on the heat conductor 4 is interconnected with the active chip 2 , and the other end of the second TSV is exposed on the surface of the package 5 .

[0043] Through the setting of the above structure, the heat on the memory chip 3 can be introduced to the active chip 2, and then a large amount of heat on the active chip 2 can be exported to the air through the seco...

Embodiment 2

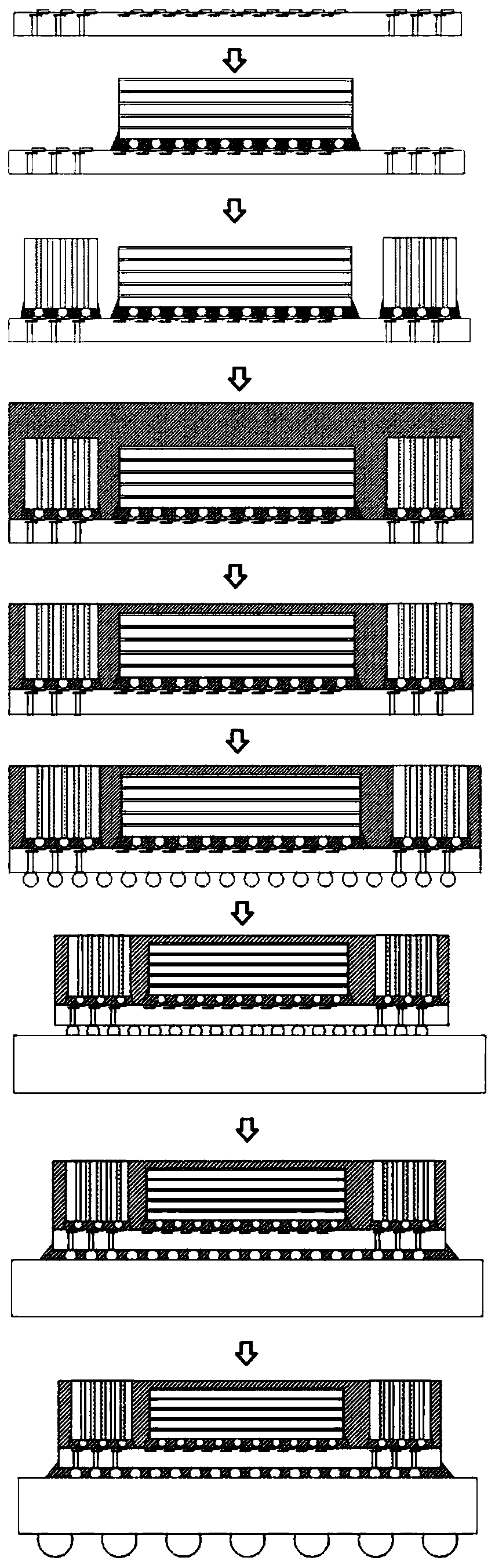

[0049] This embodiment provides a packaging process for a packaging structure for system heat dissipation, such as figure 2 As shown, the specific process is as follows:

[0050] Step 1: Mount the memory chip 3 and the heat conductor 4 with the second TSV on the same side of the active chip 2 . In the present invention, the memory chip 3 is mounted on the active chip 2 first, and then the heat conductor 4 is mounted on the active chip 2 . The memory chip 3 can be mounted on the front of the active chip 2, and can also be mounted on the back of the active chip 2; when mounted on the back, the interconnection between the active chip 2 and the memory chip 3 can be realized through leads; When it is on the front side, the back side of the memory chip 3 can be used to mount on the front side of the active chip 2. At this time, the interconnection between the memory chip 3 and the active chip 2 can be realized through leads, or the front side of the memory chip 3 can be used to be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com