Hybrid gate driving circuit

A gate drive circuit, a hybrid technology, applied in circuits, electrical components, electronic switches, etc., can solve the problems of long follow-up process, uncontrollable drive speed, and inability to meet the needs of controlling the drive speed of the slope at the same time, so as to achieve perfection Transient process, enhance anti-crosstalk ability, optimize the effect of electromagnetic interference EMI

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Below in conjunction with accompanying drawing and specific embodiment, the present invention will be further elaborated:

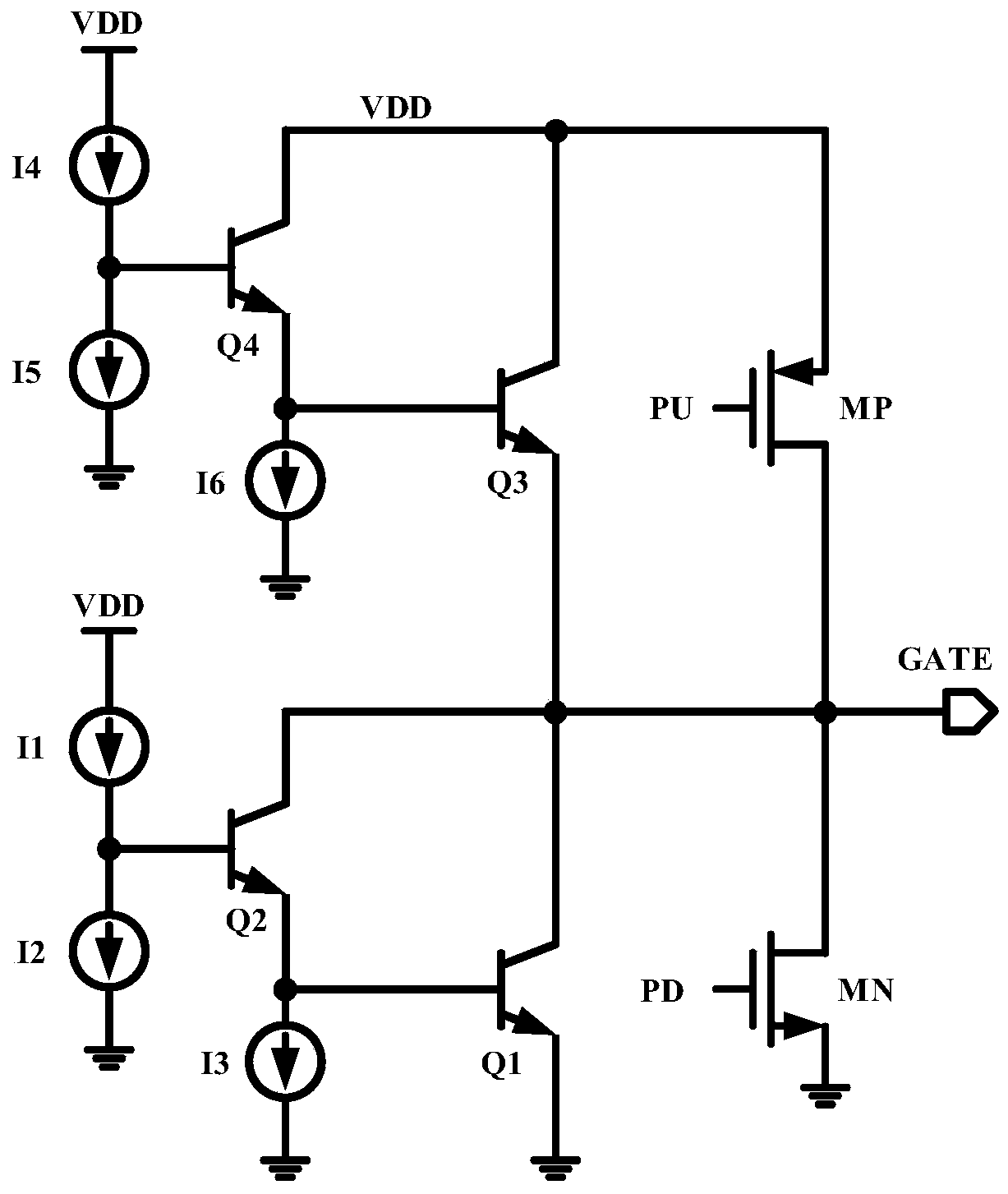

[0022] Such as Figure 4 Shown is an overall block diagram of a hybrid gate drive circuit proposed by the present invention, including a first Darlington tube, a second Darlington tube, a first Darlington tube control module, and a second Darlington tube control module. The module, the first PMOS transistor MP and the first NMOS transistor MN, the first Darlington transistor is connected between the power supply voltage VDD and the output terminal of the hybrid gate drive circuit, and is controlled by the first Darlington transistor control module; The second Darlington tube is connected between the output terminal of the hybrid gate drive circuit and the ground, and is controlled by the second Darlington tube control module; the gate of the first PMOS transistor MP is connected to the first control signal PU, and its source Connect to the power s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com