A kind of preparation method of double-layer structure silicon epitaxial wafer

A silicon epitaxial wafer, double-layer structure technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of large gap between double-layer silicon epitaxial wafers, slow rise of resistivity between layers, and consistency of intra-chip resistivity Difficult to control and other problems, to achieve the effect of improving the climb rate and satisfying the effective thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

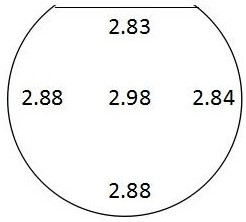

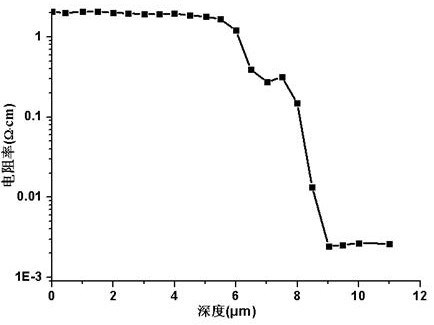

Examples

Embodiment 1

[0037] (1) Hydrogen chloride gas was introduced into the reaction chamber, and the flow rate of hydrogen chloride gas was set at 18 L / min. The residual deposition material on the graphite base of the reaction chamber was etched at high temperature, and the reaction temperature was set at 1180°C. The time was set at 1.0 min.

[0038] (2) Set the flow rate of hydrogen in the main process to 75 L / min, carry gaseous trichlorosilane into the reaction chamber, set the flow rate of trichlorosilane to 13.5 L / min, and set the deposition time to 20 sec. A layer of non-doped dense polysilicon is deposited on the surface of the seat.

[0039] (3) Load the silicon substrate on the disc-type base in the reaction chamber, and raise the temperature to 1160°C.

[0040] (4) Pass in hydrogen chloride gas, the flow rate of hydrogen chloride gas is set to 0.8 L / min, and the surface of the silicon substrate is polished, the polishing time is set to 1.0 min, and then the temperature is lowered to 1...

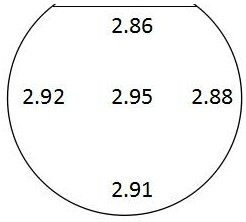

Embodiment 2

[0049] (1) Hydrogen chloride gas was introduced into the reaction chamber, and the flow rate of hydrogen chloride gas was set to 18 L / min. The residual deposited substances on the graphite base of the reaction chamber were etched at high temperature, and the reaction temperature was set to 1180 °C. The eclipse time was set to 1.0 min.

[0050] (2) Set the flow rate of hydrogen in the main process to 75 L / min, carry gaseous trichlorosilane into the reaction chamber, set the flow rate of trichlorosilane to 13.5 L / min, and set the deposition time to 20 sec. A layer of non-doped dense polysilicon is deposited on the surface of the seat.

[0051] (3) Load the silicon substrate on the disc-type base in the reaction chamber, and raise the temperature to 1160°C.

[0052] (4) Pass in hydrogen chloride gas, the flow rate of hydrogen chloride gas is set to 2.0 L / min, and the surface of the silicon substrate is polished, the polishing time is set to 1.0 min, and then the temperature is l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com