A kind of annealing method of iii-v group semiconductor wafer

A III-V, semiconductor technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult to eliminate the risk of debris, increased damage rate, proportionally increased debris risk, etc., to eliminate the risk of high temperature debris , the effect of reducing impact and reducing the risk of debris

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

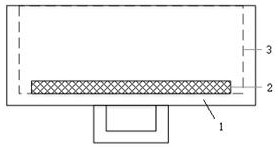

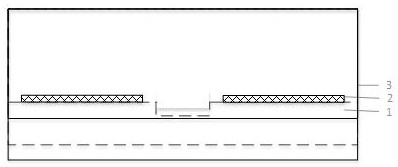

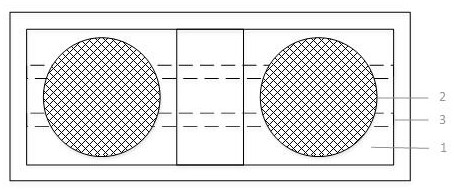

[0048] This embodiment adopts the most common annealing furnace, Figure 1 to Figure 3 shows how the wafer is loaded, such as Figure 1-Figure 3 As shown, the wafer 2 does not adopt the traditional way of placing the wafer boat in the vertical direction, but is placed horizontally on the loading table 1 made of quartz material. The table surface of the loading table 1 is treated as a smooth plane, which is consistent with The bottom surface of the wafer 1 is in full contact, and good heat conduction is realized between the wafer 2 and the loading stage 1. On the one hand, the force on the wafer 1 at high temperature is very balanced, and on the other hand, the temperature of the wafer 2 is adjusted with the load. The temperature of the wafer stage 1 changes synchronously. Since the thermal conductivity of the wafer stage is poor, its own temperature changes relatively slowly, so that the wafer 2 does not undergo a rapid temperature rise and fall. In the present embodiment, th...

Embodiment 2

[0051] The wafer loading method in this embodiment is the same as that in Embodiment 1, and will not be repeated here. The annealing temperature used in this embodiment is 420°C, Figure 5 The annealing process curve of this embodiment is shown. The first stage is a rapid heating stage, the wafer temperature rises from room temperature to 350 ° C, the heating rate is 33 ° C / min, and the heating time is about 10 min; In the initial stress release stage, the temperature is lowered to 300°C, and the cooling time is 1min; the third stage is the slow heating stage, the wafer temperature rises from 300°C to 420°C, the heating rate is 12°C / min, and the heating time is about 10min; the fourth The first stage is the constant temperature stage, the constant temperature is 420°C, and the constant temperature time is 15 minutes; the fifth stage is the slow cooling stage, the wafer temperature drops from 420°C to 300°C, the cooling rate is 12°C / min, and the cooling time is about 10 minut...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com