A programmable logic unit structure and a chip

A logic unit and programming logic technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of less combination logic and addition logic, low resource area utilization efficiency, and large number of input ports, etc., to achieve The effect of improving logic efficiency, optimizing area utilization, and improving mapping efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that even without these technical details and various changes and modifications based on the following embodiments, the technical solutions claimed in this application can also be realized.

[0051] Explanation of some concepts:

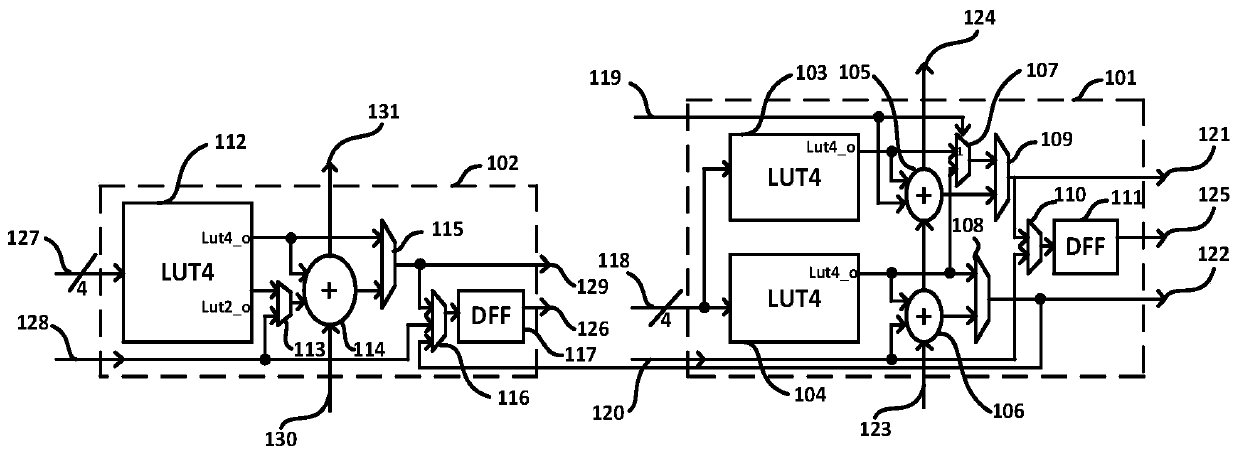

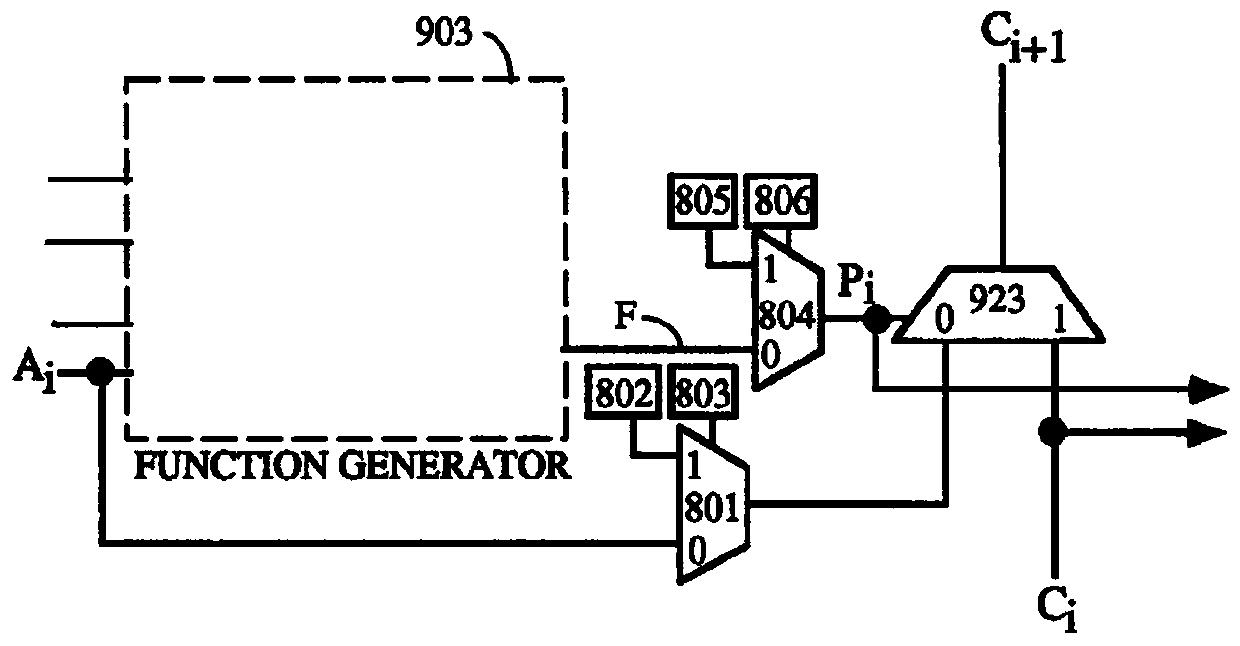

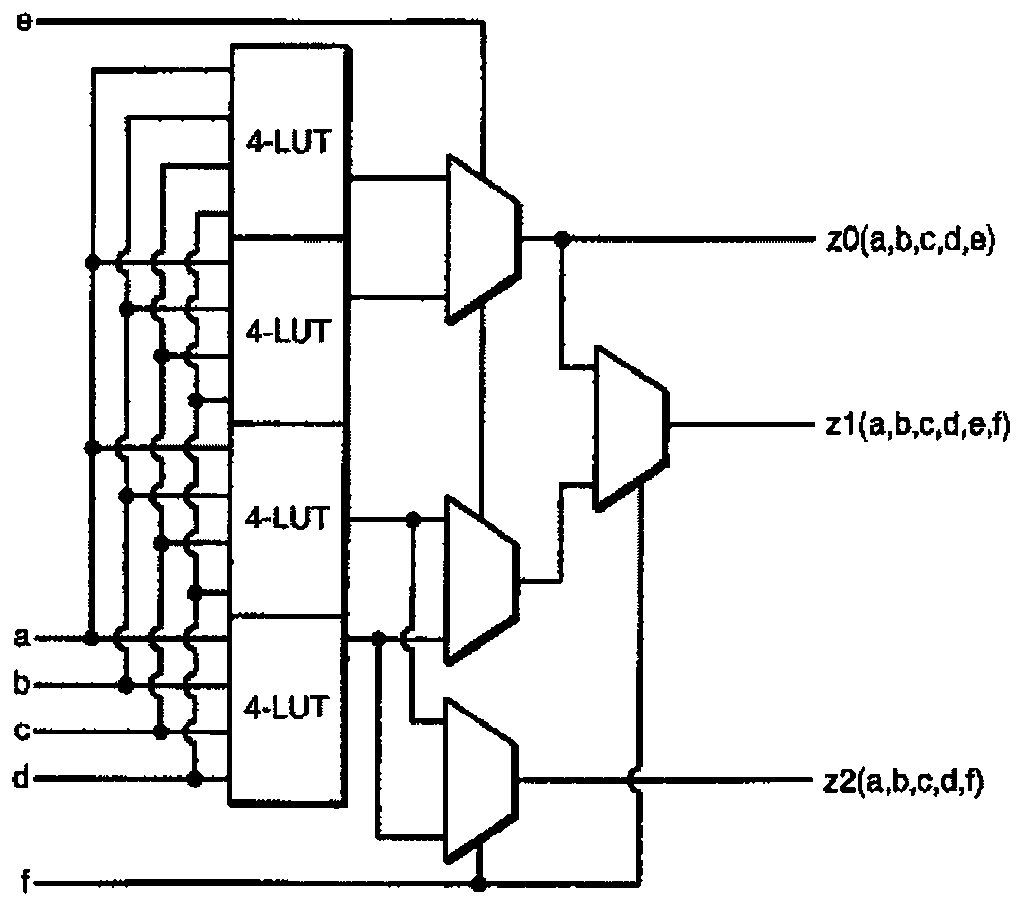

[0052] Programmable logic cell: In a programmable logic device, a programmable logic cell is usually used to implement random logic functions and sequential logic in user designs. For Field Programmable Logic Array (FPGA), most programmable logic units are composed of a certain number of look-up tables and sequential units (edge-triggered registers or level-type latches). The programmable logic cells are connected together through pre-customized metal wiring and controllable switches (programmable interconnection).

[0053] Logic unit: Logic Element, referred to as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com