A chip mipi interface loss prevention protection circuit

A technology for protecting circuits and chips, used in emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, circuit devices, etc., can solve problems such as easy damage, O damage of MC20902, etc. Durability, ease of disassembly, reduced maintenance costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other. The present invention will be further described in detail below in combination with specific embodiments.

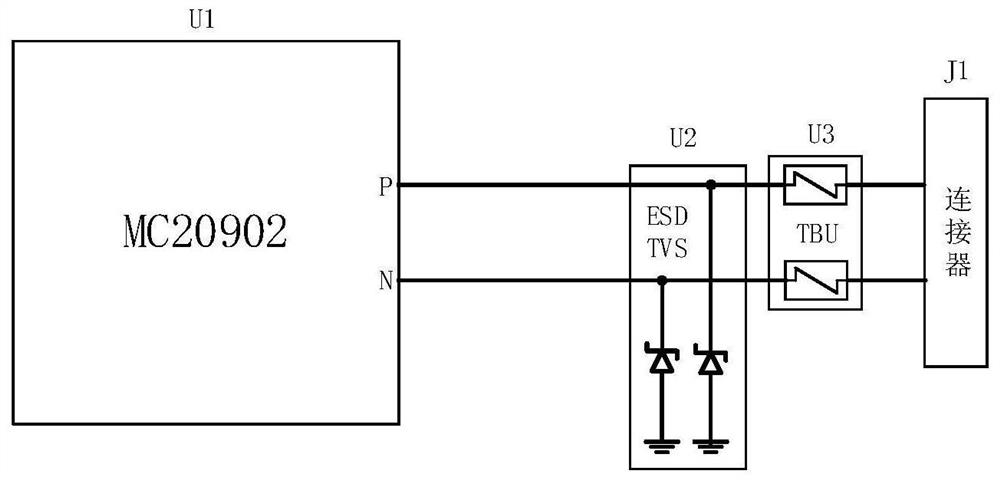

[0026] Such as figure 1 As shown, in the prior art, the chip (U1) is connected to the output interface connector (J1) through the ESD protection device (U2) and the transient blocking element (U3). The above-mentioned chip, ESD protection device, transient blocking element and output inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com