High-performance low-temperature-sintering laminated chip varistor material

A low-temperature sintering and piezoresistor technology, which is applied to piezoresistors, piezoresistor cores, etc., can solve problems such as poor performance of piezoresistor materials, achieve good application prospects, reasonable formula ratio, and improve sintering density sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0019] Embodiment 1: (1) adopt following raw material composition and content preparation material thereof:

[0020] Table 1: Formula table of embodiment 1 (unit: mol)

[0021] ZnO

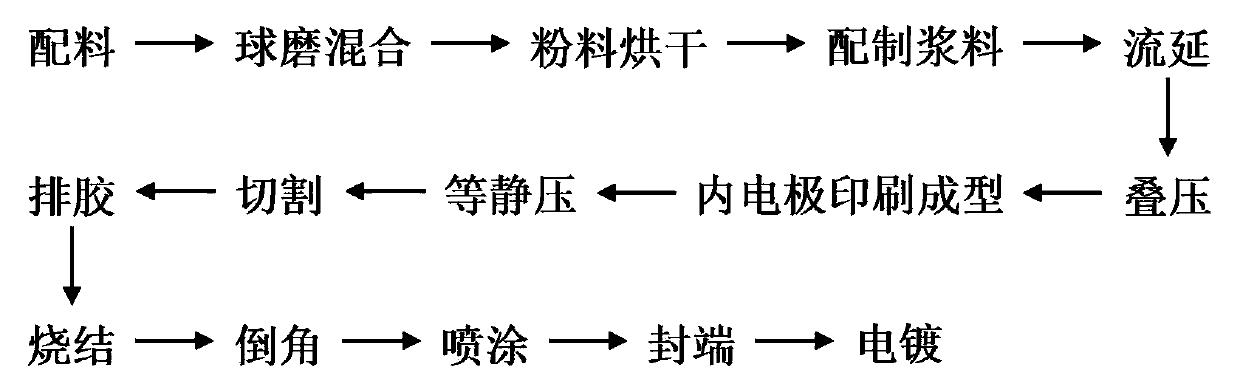

[0022] (2) Weigh the raw materials according to the formula ratio in Table 1, mix the raw materials by ball milling, drying, crushing and sieving to obtain high-performance low-temperature sintered laminated chip varistor materials, and then prepare them according to the manufacturing process of laminated chip capacitors Chip varistors, that is, the varistor materials are prepared by slurry preparation, casting, lamination, molding, isostatic pressing, cutting, debinding, sintering, chamfering, spraying, capping, electroplating, etc., to obtain laminated varistors. Layer chip varistors, in which the thickness of the cast film is 50 μm, the isostatic pressure is 32 MPa and the pressure is maintained for 15 minutes, the sintering temperature is 915 ° C and kept for 6 hours, and then naturall...

Embodiment 2

[0023] Embodiment 2: (1) adopt following raw material composition and content preparation material thereof:

[0024] Table 2: Formula table of embodiment 2 (unit: mol)

[0025] ZnO

[0026] (2) Weigh the raw materials according to the formula ratio in Table 2, and mix the raw materials by ball milling, drying, crushing and sieving to obtain high-performance low-temperature sintered laminated chip varistor materials, and then prepare them according to the manufacturing process of laminated chip capacitors Chip varistors, that is, the varistor materials are prepared by slurry preparation, casting, lamination, molding, isostatic pressing, cutting, debinding, sintering, chamfering, spraying, capping, electroplating, etc., to obtain laminated varistors. Layer chip varistors, in which the thickness of the cast film is 50 μm, the isostatic pressure is 32 MPa and the pressure is maintained for 15 minutes, the sintering temperature is 915 ° C and kept for 6 hours, and then na...

Embodiment 3

[0027] Embodiment 3: (1) adopt following raw material composition and content preparation material thereof:

[0028] Table 3: Formula table of embodiment 3 (unit: mol)

[0029] ZnO

[0030] (2) Weigh the raw materials according to the formula ratio in Table 3, mix the raw materials by ball milling, drying, crushing and sieving to obtain high-performance low-temperature sintered laminated chip varistor materials, and then prepare them according to the manufacturing process of laminated chip capacitors Chip varistors, that is, the varistor materials are prepared by slurry preparation, casting, lamination, molding, isostatic pressing, cutting, debinding, sintering, chamfering, spraying, capping, electroplating, etc., to obtain laminated varistors. Layer chip varistors, in which the thickness of the cast film is 50 μm, the isostatic pressure is 32 MPa and the pressure is maintained for 15 minutes, the sintering temperature is 915 ° C and kept for 6 hours, and then natura...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com