Three-dimensional memory and manufacturing method thereof

A manufacturing method and memory technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as poor performance of three-dimensional memory, meet the requirements of reducing flatness, improve production efficiency, and ensure performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

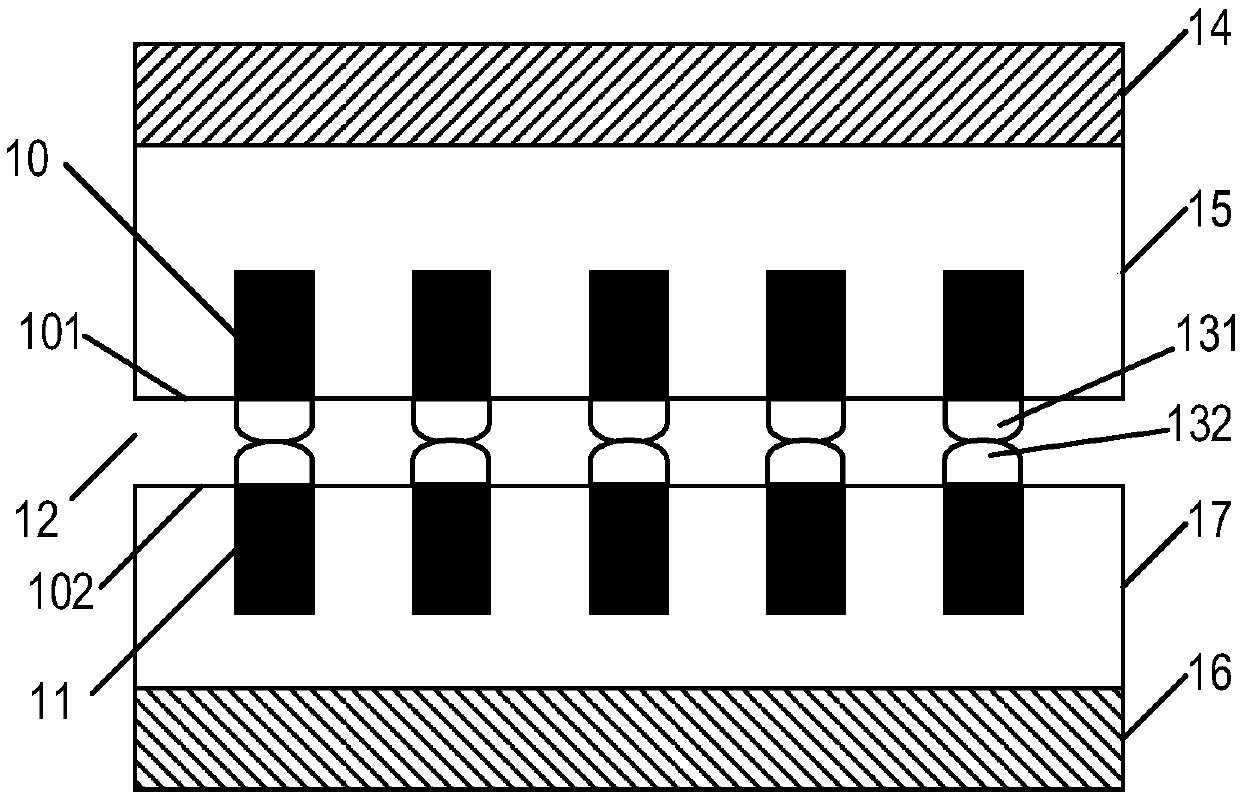

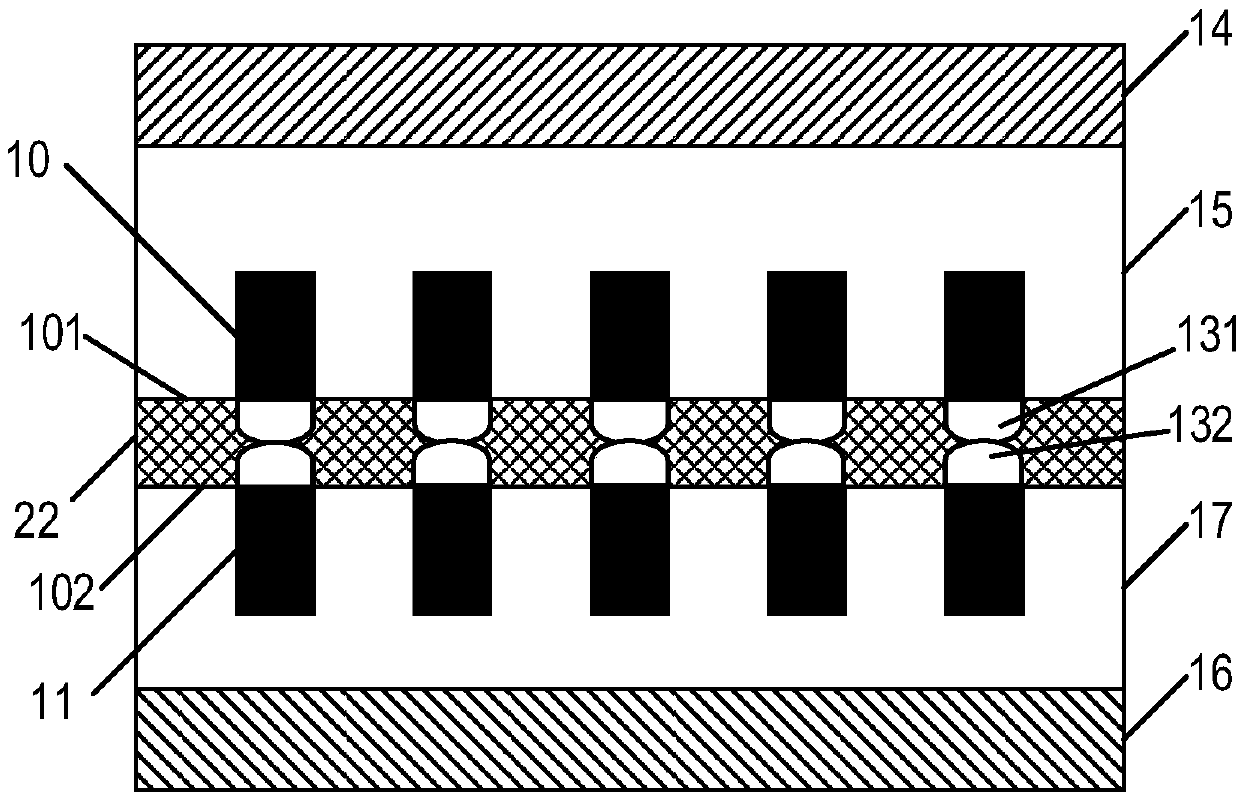

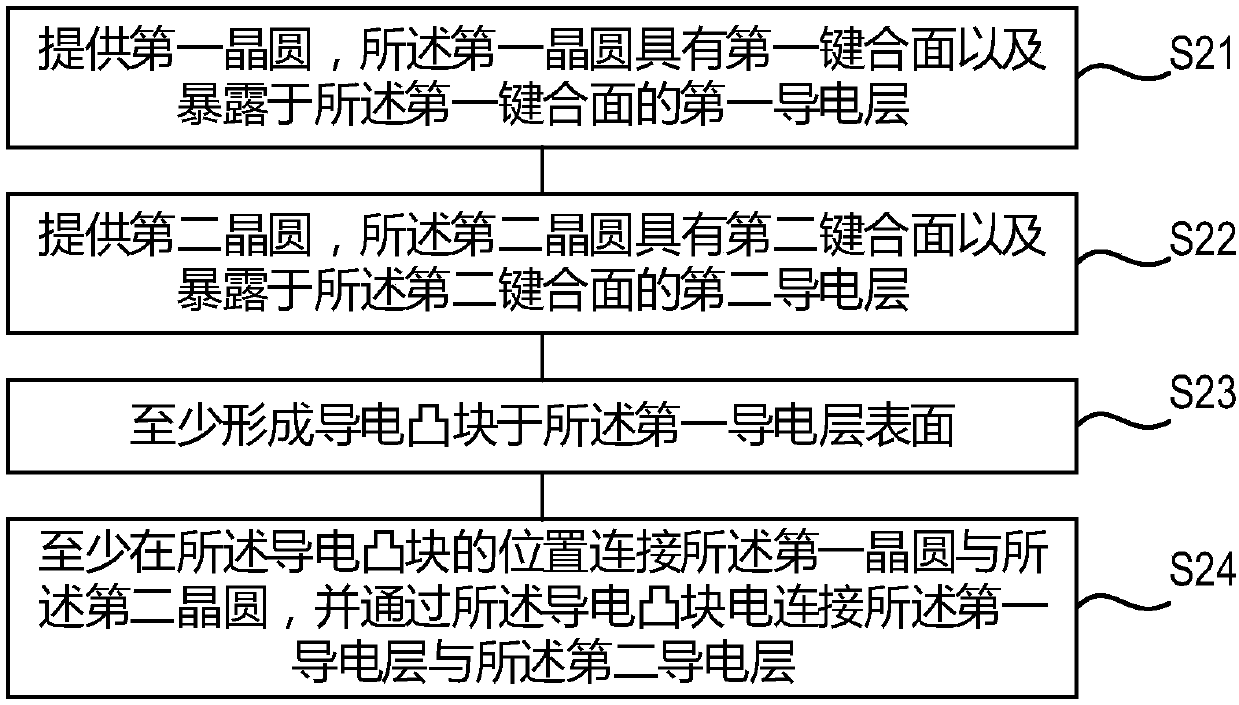

[0051] The specific implementation of the three-dimensional memory and its manufacturing method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0052] In the three-dimensional memory, the memory array wafer and the peripheral circuit wafer are electrically connected by bonding. Usually, the bonding of the memory array wafer and the peripheral circuit wafer is direct contact bonding between dielectric layers. The specific way of bonding the storage array wafer and the peripheral circuit wafer is: at a specific bonding temperature, the bonding surface of the storage array wafer is in contact with the bonding surface of the peripheral circuit, And use external pressure to bond the two wafers together.

[0053] However, this method of relying on the direct contact of the dielectric layers on the two wafers to achieve bonding has at least the following two defects: on the one hand, since the dielectric layers on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com