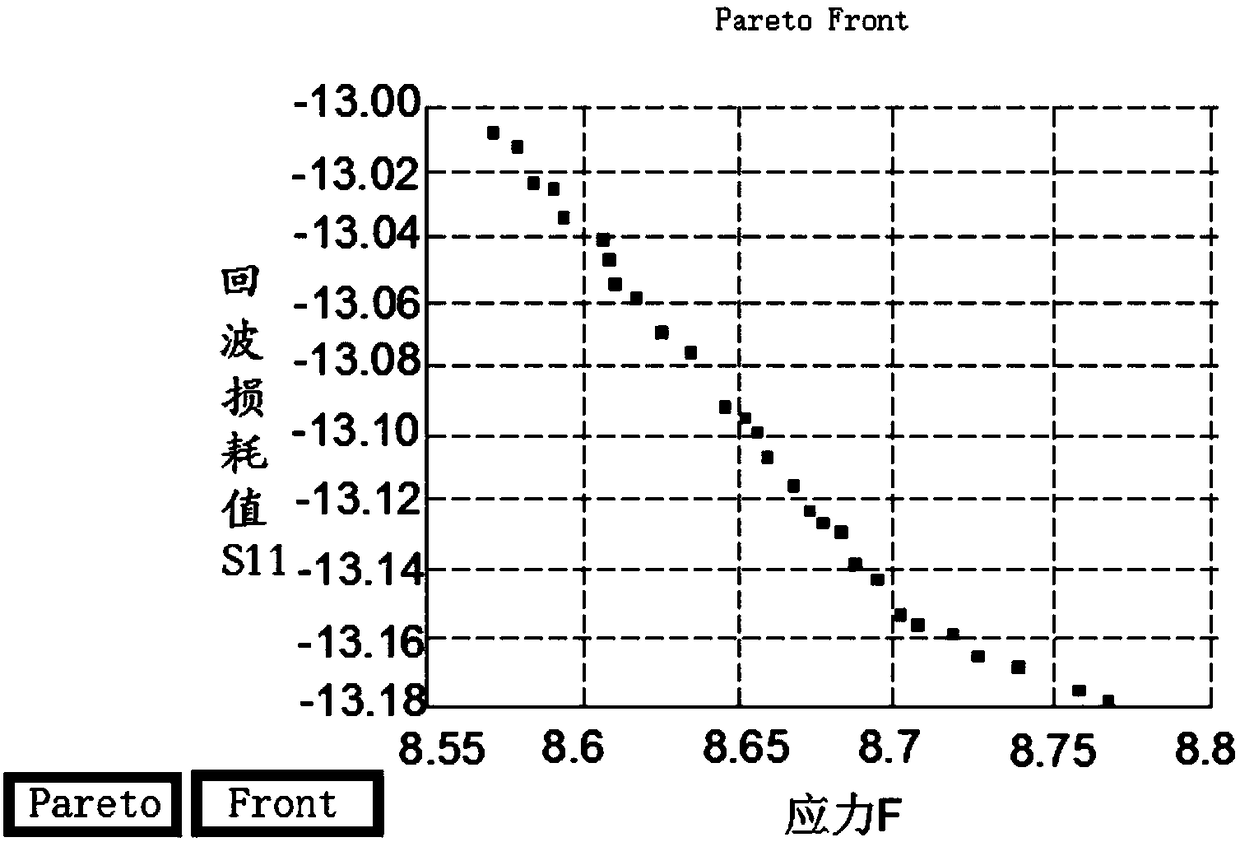

Optimization method of random vibration stress and return loss of chip package solder joints

A return loss and random vibration technology, applied in design optimization/simulation, special data processing applications, instruments, etc., can solve the problems of not taking into account the vibration analysis and signal integrity of solder joints, so as to improve reliability and signal integrity , random vibration stress and callback loss reduction, and the effect of inhibiting premature convergence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

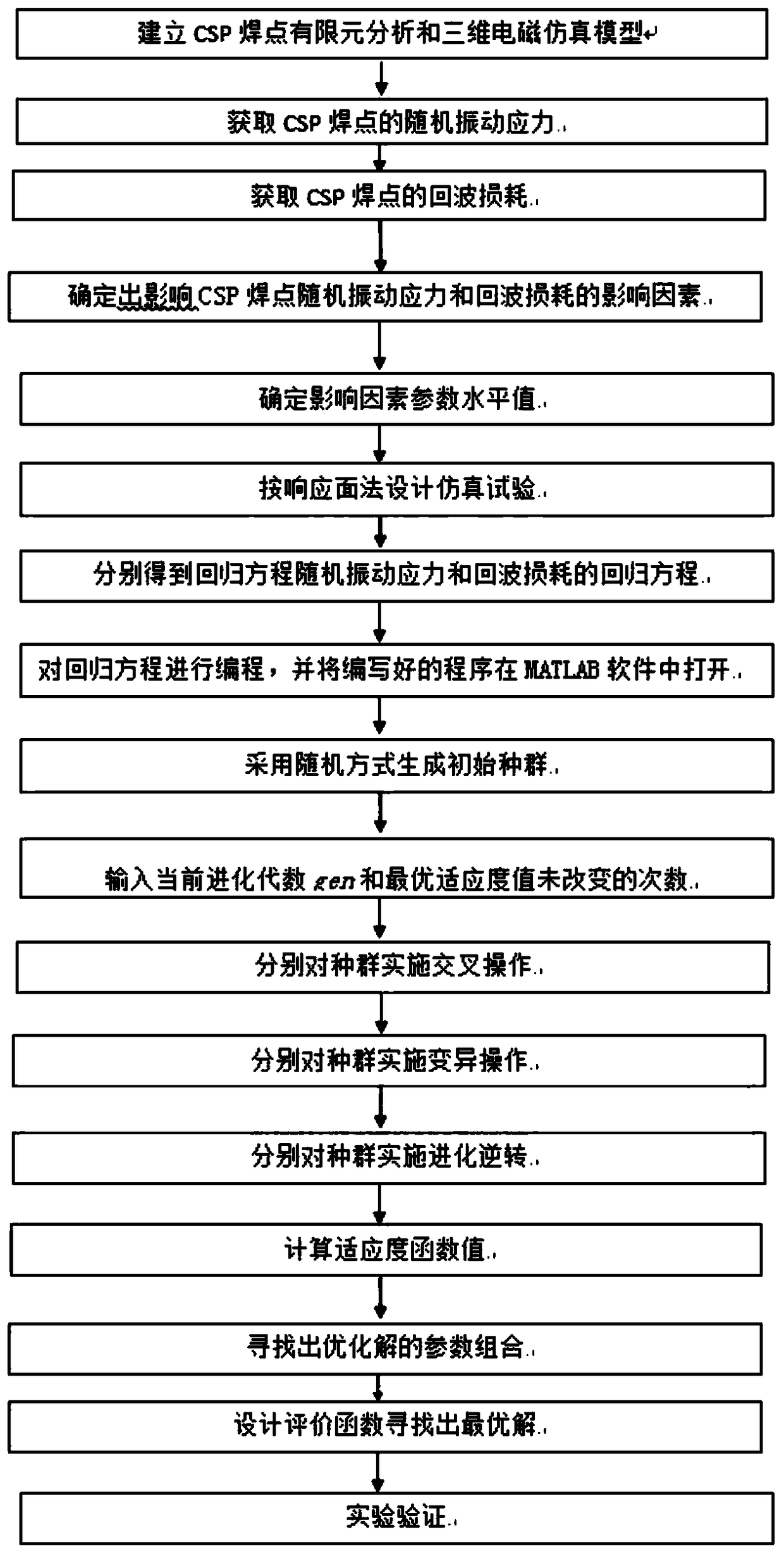

[0064] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0065] Such as Figure 1 to Figure 14 As shown, the method for optimizing random vibration stress and return loss of chip packaging solder joints according to the present invention comprises the following steps:

[0066] Step 1: Establish a CSP solder joint finite element analysis model and a three-dimensional electromagnetic simulation model: the model is an organic substrate 1, a solder joint 2 and a printed circuit board 3 stacked sequentially from top to bottom;

[0067] Step 2: Obtain the random vibration stress of the CSP solder joint: impose constraints on the model built in step 1), conduct analysis under random vibration loading conditions, and then use ANSYS software to simulate and analyze the model to obtain the stress distribution of the CSP solder joint;

[0068] Step 3: Obtain the return loss of the CSP solder joint: apply wave port exci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com