A unidirectional carrier photoelectric mixer and electromagnetic wave phased array antenna receiving front end

A single-line carrier and mixer technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of large photoelectric mixing loss, low device speed, low frequency, etc., and achieve the effect of large bandwidth loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

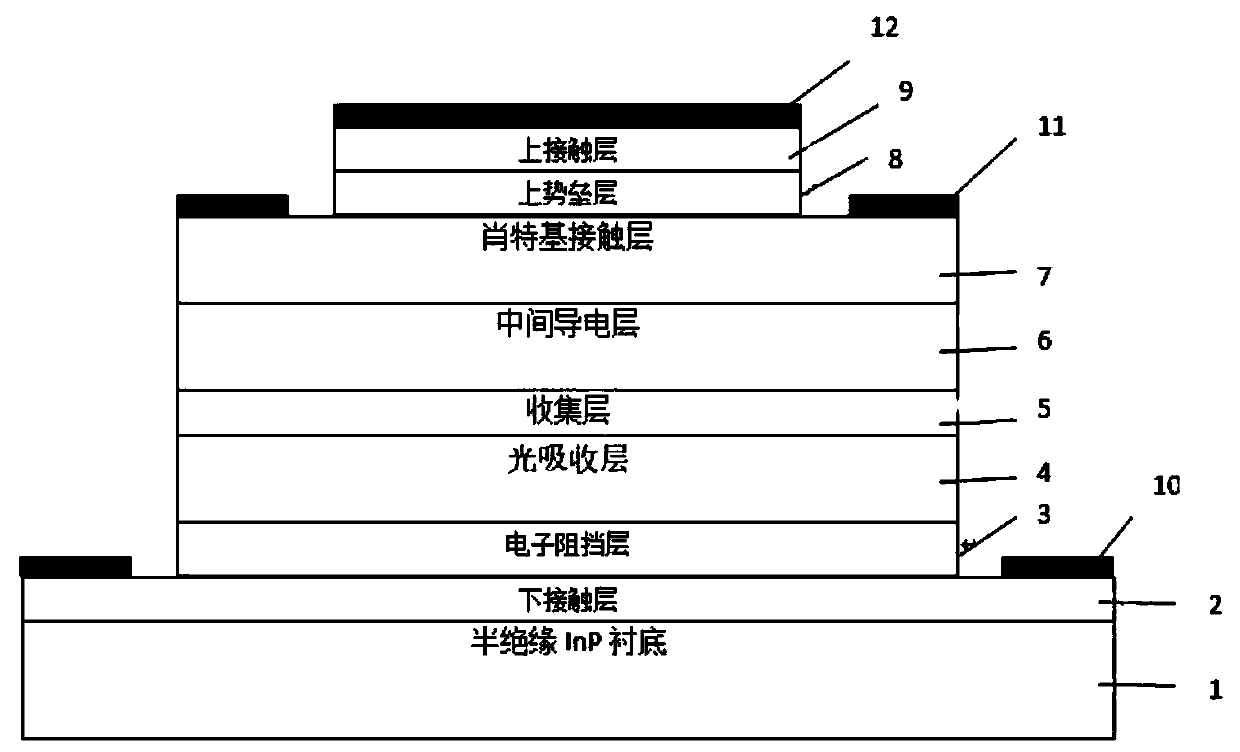

[0091] figure 1 It is a schematic diagram of the epitaxial layer structure of the single row carrier photoelectric mixer in the specific embodiment 1 of the present invention. combine figure 1 As shown, in this embodiment, the single row carrier optoelectronic mixer includes:

[0092] The semi-insulating substrate 1 is an InP semi-insulating substrate;

[0093] The P-type heavily doped lower contact layer 2 located on the upper surface of the semi-insulating substrate is a P-type heavily doped InGaAs layer;

[0094] The P-type heavily doped electron blocking layer 3 located on the upper surface of the P-type heavily doped lower contact layer is a P-type heavily doped InP layer;

[0095] The lower electrode metal layer 10 located on the upper surface of the P-type heavily doped lower contact layer and on both sides of the P-type heavily doped electron blocking layer;

[0096] The light absorbing layer 4 located on the upper surface of the P-type heavily doped electron block...

Embodiment 2

[0115] combine Figure 6 As shown, the single row carrier opto-electric mixer consists of:

[0116] The semi-insulating substrate 1 is an InP semi-insulating substrate;

[0117] The P-type heavily doped lower contact layer 2 located on the upper surface of the semi-insulating substrate is P-type heavily doped InGaAs;

[0118] The P-type heavily doped electron blocking layer 3 located on the upper surface of the P-type heavily doped lower contact layer is a P-type heavily doped InP layer;

[0119] The lower electrode metal layer 10 located on the upper surface of the P-type heavily doped lower contact layer and on both sides of the P-type heavily doped electron blocking layer;

[0120] The light absorbing layer 4 located on the upper surface of the P-type heavily doped electron blocking layer is a P-type gradiently doped InGaAs layer;

[0121] The collection layer 5 located on the upper surface of the light absorption layer is a low-doped N-type InP layer;

[0122] The N-ty...

Embodiment 3

[0144] like Figure 9 As shown in , the unit in the dotted box is a specific implementation method of delay / phase shift network and synthesis. Output signal e after photoelectric mixing m,i (i=0,1,2,...N) first pass through the low noise amplifier LNA i (i=0,1,2,...N) to amplify, and then pass through the electric phase shifter / delay device D i (i=0,1,2,...N) Delay different channels so that each channel outputs an electrical signal e after frequency conversion mp,i The phases of (i=0,1,2,...N) are all at time t, and the electrical signals of different channels are superimposed in the same phase in the power combiner, and then the signals are sent to the signal processing unit for further signal processing.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com