Shield grid DMOS device

A shielding gate and device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of device reliability reduction, switching loss increase, gate-source capacitance increase, etc., to improve switching speed and withstand voltage level, Effect of reducing switching loss and improving contradictory relationship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

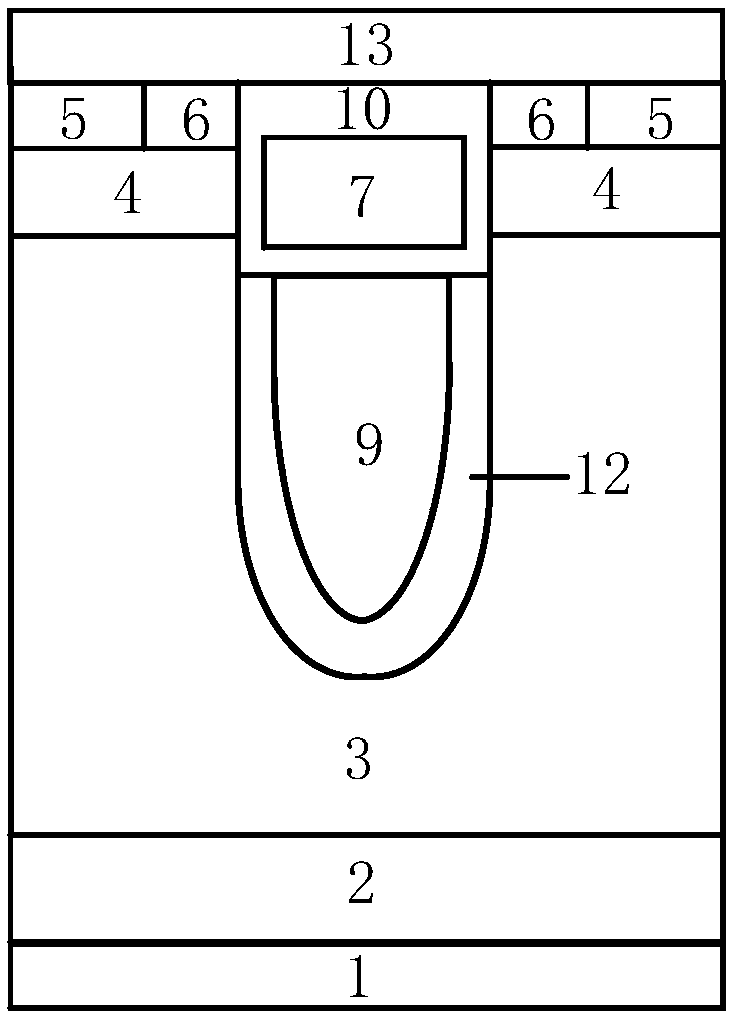

[0022] This embodiment provides a figure 2 The shielded gate DMOS device shown includes a metallized drain 1, a first conductivity type semiconductor heavily doped substrate 2, a first conductivity type semiconductor drift region 3, and a metallization source 13 that are sequentially stacked from bottom to top; The upper layer of the first conductivity type semiconductor drift region 3 has a groove gate structure and a second conductivity type semiconductor body region 4, and the second conductivity type semiconductor body region 4 is located on both sides of the groove gate structure and is in contact with the groove gate structure; The upper layer of the second conductivity type semiconductor body region 4 has a second conductivity type semiconductor heavily doped contact region 5 and a first conductivity type semiconductor heavily doped source region 6, and the first conductivity type semiconductor heavily doped source region 6 is connected to the groove Gate structure con...

Embodiment 2

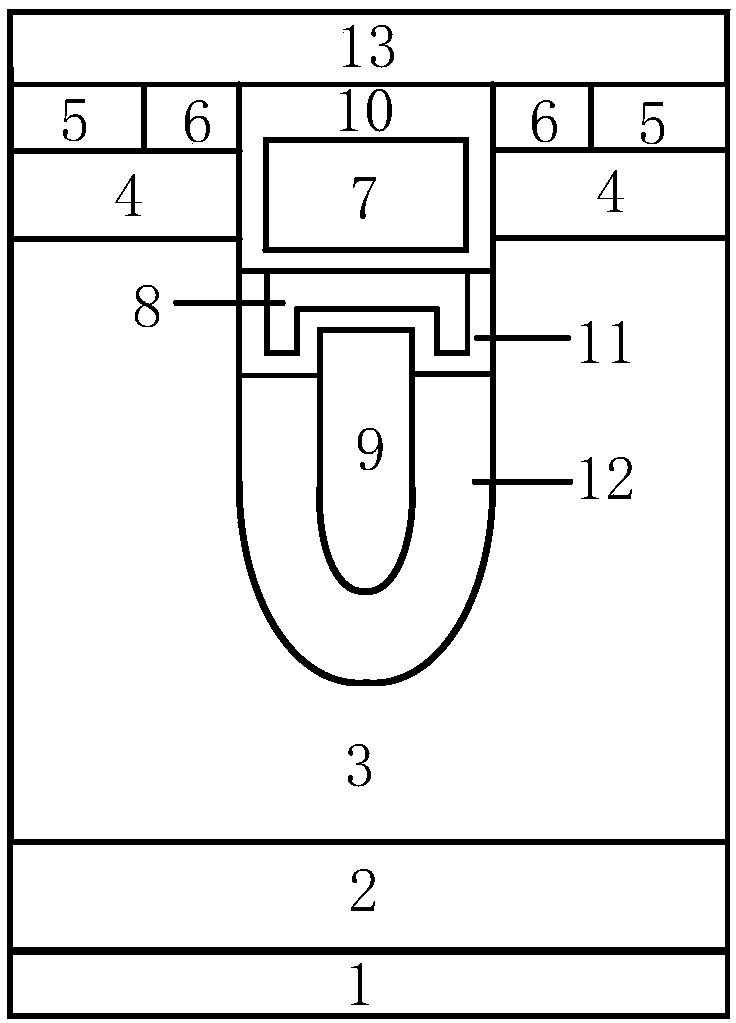

[0027] The embodiment of the present invention is different from the embodiment 1 in that: the shielding gate electrode 9 and the third dielectric layer 12 extend to the bottom of the first conductivity type semiconductor drift region 3, so that the shielding gate electrode 9 is located inside the third dielectric layer 12, The lower surface of the third dielectric layer 12 is in contact with the heavily doped substrate 2 of the first conductivity type semiconductor, such as image 3 shown. This embodiment can achieve a higher doping concentration in the drift region, further reducing the on-resistance of the device.

Embodiment 3

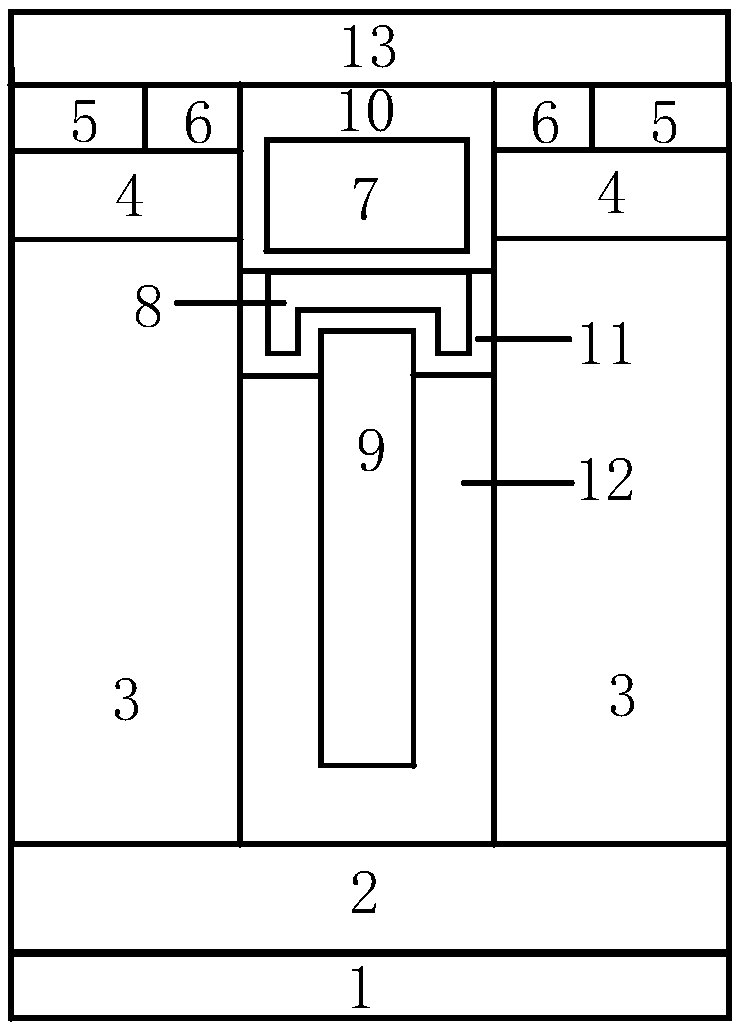

[0029] The difference between the embodiment of the present invention and the embodiment 1 is that the "inverted U-shaped" floating gate electrode 8 is replaced by a rectangular floating gate electrode 8, and the rest of the structure is the same as that of the embodiment 1, as shown in Figure 4 shown. Compared with Embodiment 1, the lateral width of the shielding gate electrode 9 in this embodiment is larger, so the manufacturing process requires less technical level, and the manufacturing process of the rectangular floating gate electrode is simple, which reduces the difficulty of the process. Moreover, the structure can properly reduce the overlapping area between the floating gate electrode and the shielding gate electrode, so as to reduce the total series capacitance value, further reduce the gate-source capacitance, and reduce switching loss.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com