Single-sided light emitting wafer-level chip scale packaging (CSP) structure and preparation method thereof

A wafer-level chip and single-sided light emission technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, and electrical solid-state devices, can solve the problems of device reliability and uniformity degradation, poor heat dissipation of light-emitting chips, and increased device costs. , to achieve the effects of improving reliability and uniformity, improving device yield, and high density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

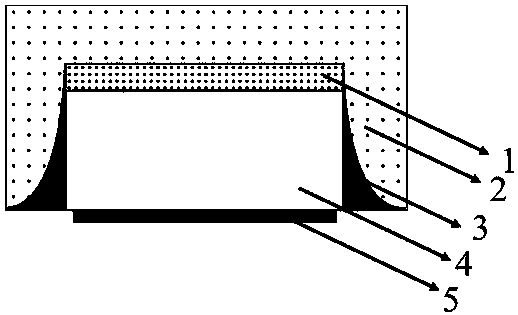

[0048] In this embodiment, the single-sided light-emitting wafer-level chip-level CSP packaging structure, such as figure 1 As shown, a chip 4 and a contact electrode 5 arranged on the chip 4 are included, and a first concentration fluorescent layer 1 is arranged on the light-emitting surface of the chip 4 to form a package A; four sides of the package A are provided with aluminum oxide The reflective wall 3 formed by the aggregation of insulating particles forms a package B; a second concentration fluorescent layer 2 is provided on the top and side surfaces of the package B to form a wafer-level chip-scale packaging structure with light output from one side; the first concentration fluorescent The phosphor concentration in the layer is denoted as w 1 , the phosphor concentration in the second concentration phosphor layer is denoted as w 2 , then w 1 >w 2 ; In this embodiment, the fluorescent layers of the first concentration fluorescent layer 2 and the second concentration f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Side wall thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com