LSTM (Long Short-Term Memory) forward direction operation accelerator based on FPGA (Field Programmable Gate Array)

An accelerator and hardware accelerator technology, applied in complex mathematical operations, instruments, calculations, etc., can solve problems such as limited promotion, long programming development cycle, and inability to modify circuit logic, and achieve the effect of improving computing performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

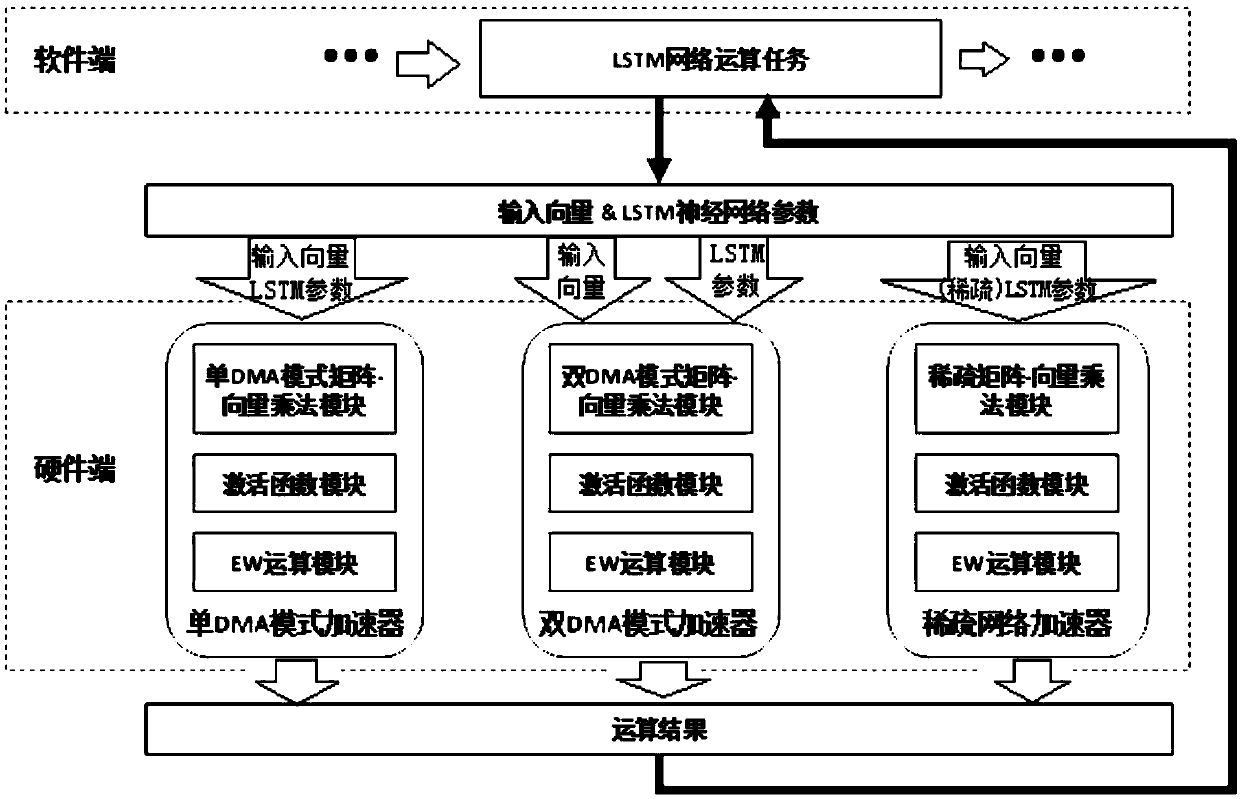

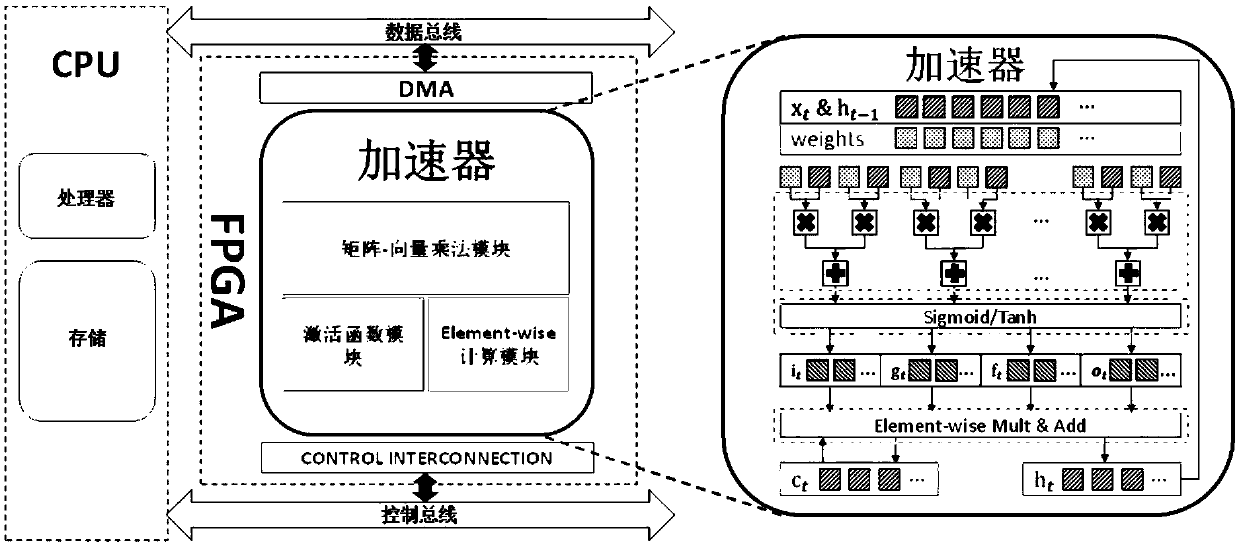

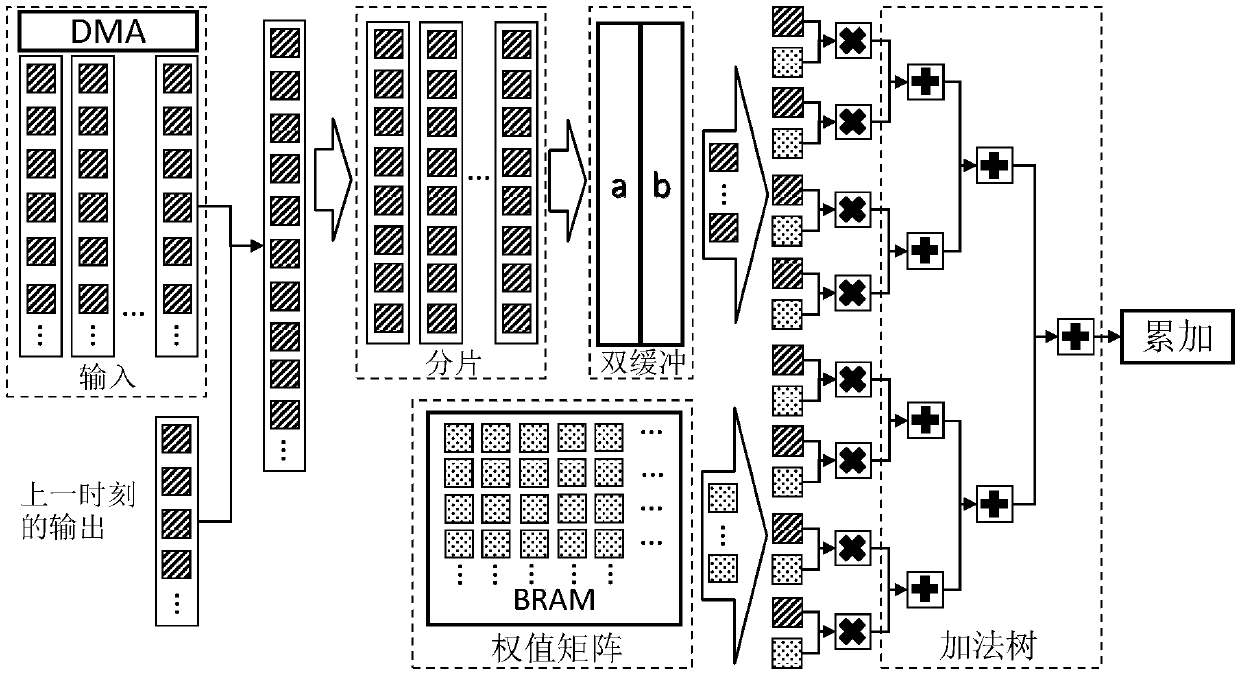

[0046] figure 1 It is a working schematic diagram of the LSTM neural network forward computing accelerator system based on FPGA, which is divided into software side and hardware side. In the specific application tasks performed on the software side, when it is necessary to use the LSTM neural network for forward computing, upload the computing tasks to It is completed on the FPGA hardware accelerator, and the calculation results of the hardware are sent back to the software side for subsequent operations. According to the parameter scale of the LSTM network, different hardware accelerators are used: when the on-chip storage resources of the FPGA are sufficient to cache all LSTM parameters, a single DMA mode hardware accelerator is used, and all parameters are cached on the chip at one time; when the LSTM parameter scale exceeds When the on-chip storage capacity of the FPGA is used, the dual DMA mode hardware accelerator is used, and some parameters required for each calculatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com