Multi-channel-based high-speed ADC phase self-correcting method

A self-calibrating, multi-channel technology, applied in analog/digital conversion calibration/testing, code conversion, electrical components, etc., which can solve the problems of difficult to correct phase consistency, difficult to guarantee phase consistency, and non-adjustable clock phase. Achieve the effect of adjustable synchronization accuracy, low power consumption and small size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] A method for phase self-calibration based on a multi-channel high-speed ADC, mainly comprising the following steps:

[0046] Step E1: data acquisition, each channel performs data acquisition on the analog signal, and then sends the corresponding signal to the FPGA, and the FPGA performs FFT transformation on each channel to extract the phase value of each channel;

[0047] Step E2: Select a reference channel and calculate the phase difference of each channel according to the reference channel;

[0048] Step E3: Calculate the correction value, perform self-calibration, calculate the correction value of each channel and perform correction to ensure that the difference of all channels is within 3 degrees; send the calibration command "calibration", and the FPGA starts to perform self-calibration after receiving the decoded command, To ensure that the phase difference between all boards is consistent.

[0049] Acquisition and real-time signal processing modules based on mu...

Embodiment 2

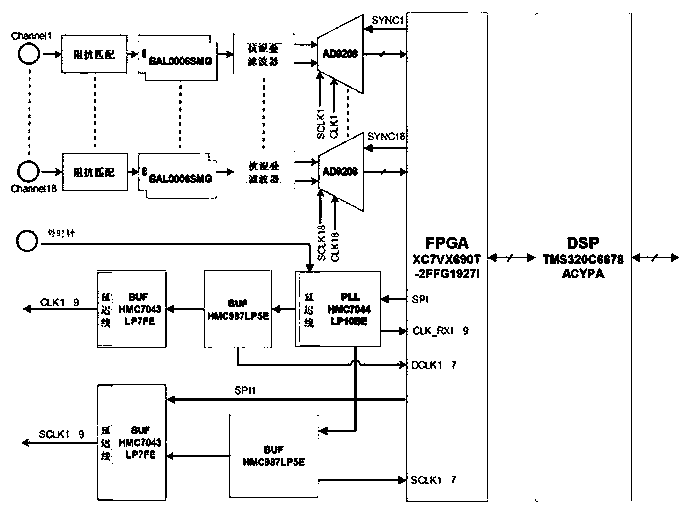

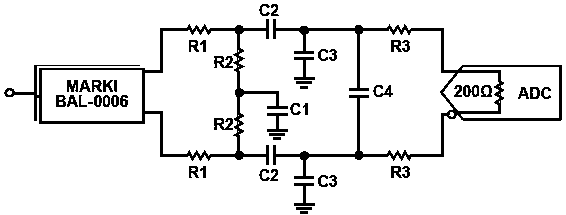

[0053] This embodiment is further optimized on the basis of Embodiment 1. The model of the ADC acquisition system is AD9208, the model of the FPGA system is XC7VX690T-2FFG1927I, the model of the DSP is TMS320C6678ACYPA, and the model of the clock system is HMC7044 .

[0054] The signal processing module of the present invention adopts a high-speed serial ADC device, has the advantages of high sampling rate, can directly collect radio frequency signals, wide bandwidth of input analog signals, small size, high real-time performance, and good synchronization accuracy; the present invention can collect radio frequency direct sampling The frequency of the signal can reach 5GHz; the sampling rate is high, up to 3Gsps; based on the array design, the real-time performance of signal processing is high; the data line of the analog-to-digital connection is small, the signal integrity is good, and the complexity of the system is reduced. Better practicality.

[0055] Other parts of this ...

Embodiment 3

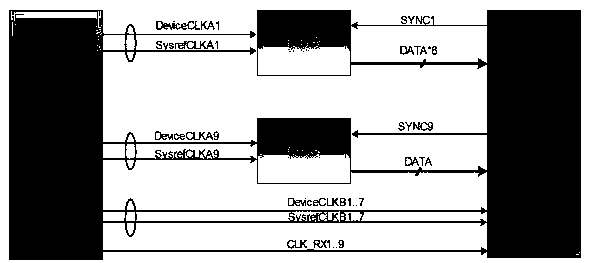

[0057] This embodiment is further optimized on the basis of Embodiment 2, the clock includes DeviceCLKA, SysrefCLKA, SYNC; the DeviceCLKA is a sampling clock, and the SysrefCLKA indicates the edge of DeviceCLKA as a reference for the deterministic delay of multiple devices; The above SYNC is used to establish a data transmission path between ADC and FPGA; data exchange is performed between each board through a dedicated communication interface; for example Figure 6 As shown, after the ADC quantizes and encodes the analog signal, the parameters of the JESD204B link are configured; the ADC and the FPGA establish a data transmission path, start normal acquisition, and send the data to the FPGA, and the FPGA preprocesses the data. Send the data to the DSP through the SRIO of the X8 for further processing. If the DSP processing result needs to be sent, it will be sent to the external device or the data central station through the Gigabit Ethernet port of the DSP.

[0058] For the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com