Ultra-low-power-consumption asynchronous successive approximation register type analog-to-digital converter

An asynchronous successive approximation, analog-to-digital converter technology, applied in the direction of analog-to-digital converter, analog-to-digital conversion, code conversion, etc., can solve the problems of low linearity and accuracy, high power consumption, large area and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

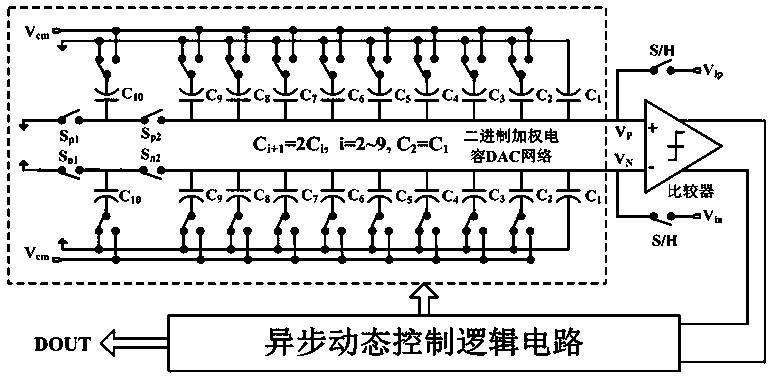

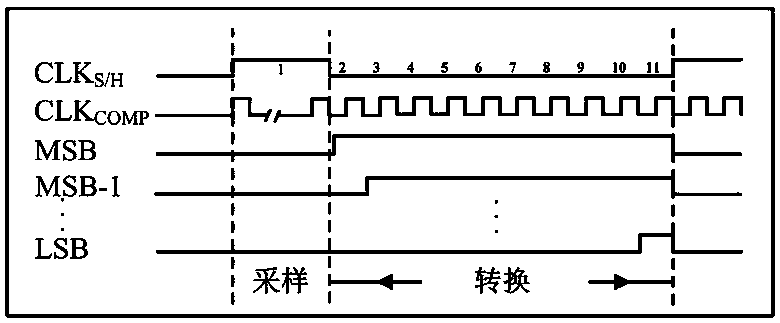

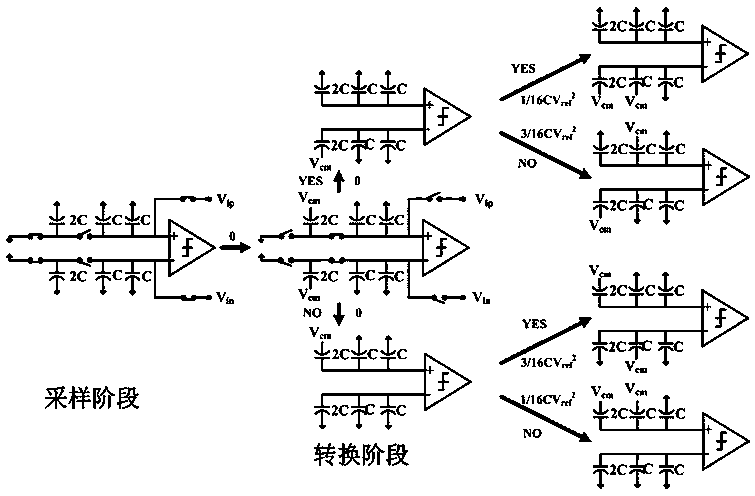

[0039] The present invention aims at the shortcomings of the traditional ultra-low power asynchronous successive approximation register type analog-to-digital converter, and makes improvements in the prior art, that is, the present invention provides a 10-bit ultra-low power consumption device applied to wireless sensor network chips Asynchronous successive-approximation register-based analog-to-digital converters achieve nanowatt-level power consumption while improving linearity.

[0040] The application principle of the present invention will be described in detail below in conjunction with the accompanying drawings.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com