A Hardware System for Fast Realization of 8x8dct Transformation

A hardware system, 8x8dct technology, applied in the direction of electrical components, image communication, digital video signal modification, etc., can solve the problems of hardware design parallelism limit, etc., to reduce algorithm complexity, avoid transposition operation, and reduce hardware area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

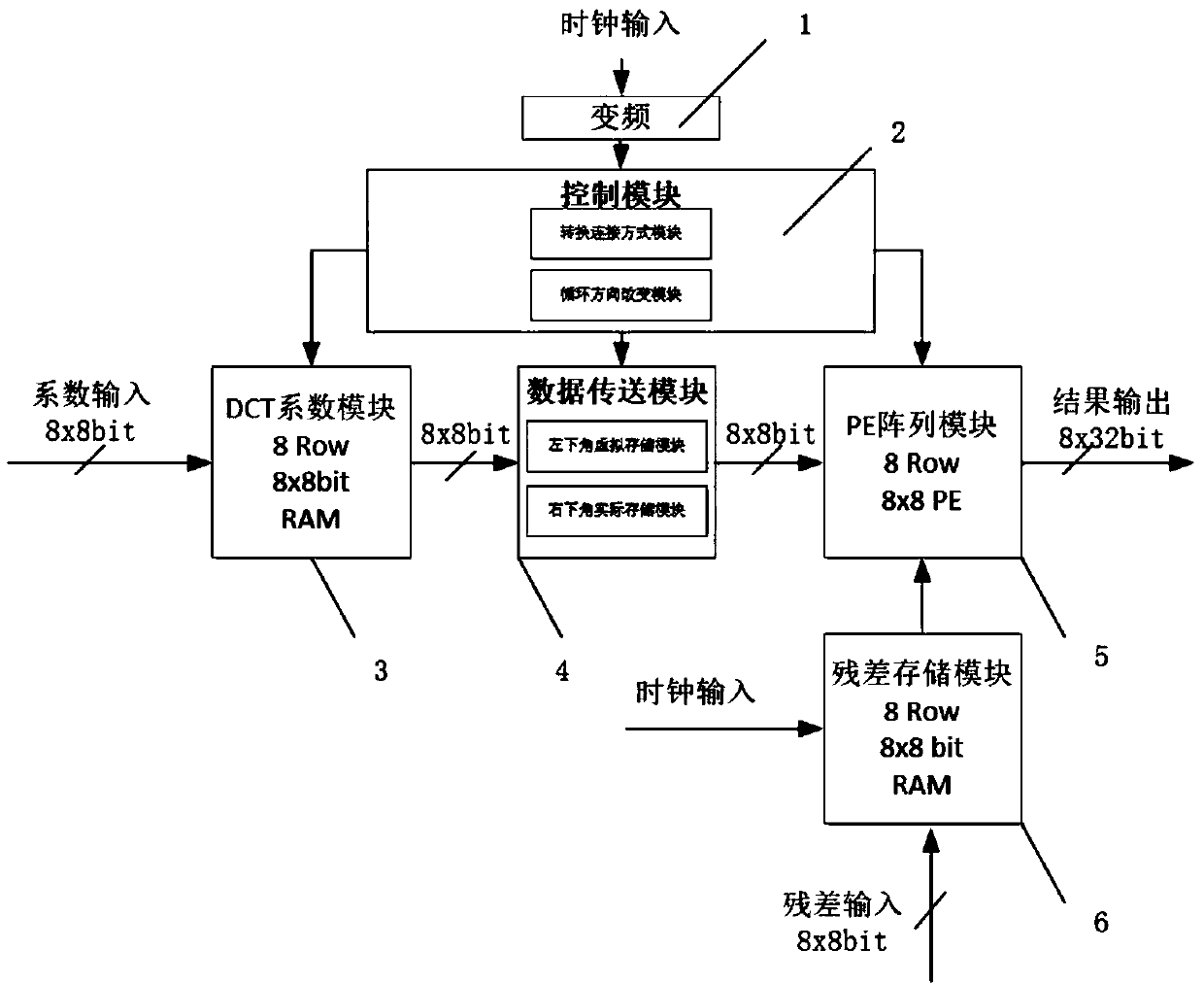

[0032] Such as figure 1 As shown, this embodiment provides a hardware system for quickly implementing 8x8DCT transformation, including a control module, a DCT coefficient module, a data transmission module, a PE array module, and a residual storage module;

[0033] The DCT coefficient module is connected to the control module and the data transmission module, and the DCT coefficient module receives the clock-synchronized DCT coefficient sent from the outside, and performs data circulation and output operations under the control of the control module;

[0034] The data transmission module is connected to the control module, the DCT coefficient module, and the PE array module, and the data transmission module receives the coefficient output by the DCT coefficient module, and makes the DCT coefficient module transmit the coefficient under the control of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com