A method of manufacturing a semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as increased difficulty in manufacturing process, easy generation of thermal stress, mismatch of thermal expansion coefficients, etc., and achieve reduction Effect of thermal stress, improvement of production efficiency, effect of guaranteed performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

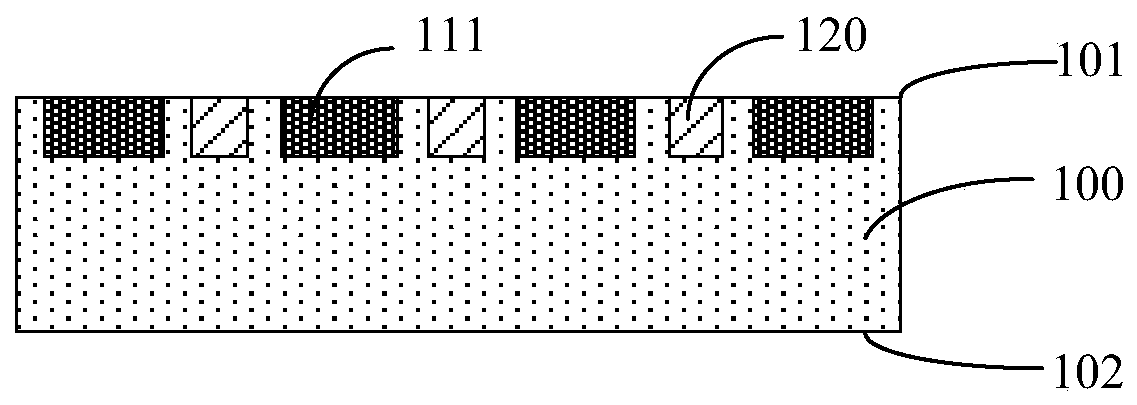

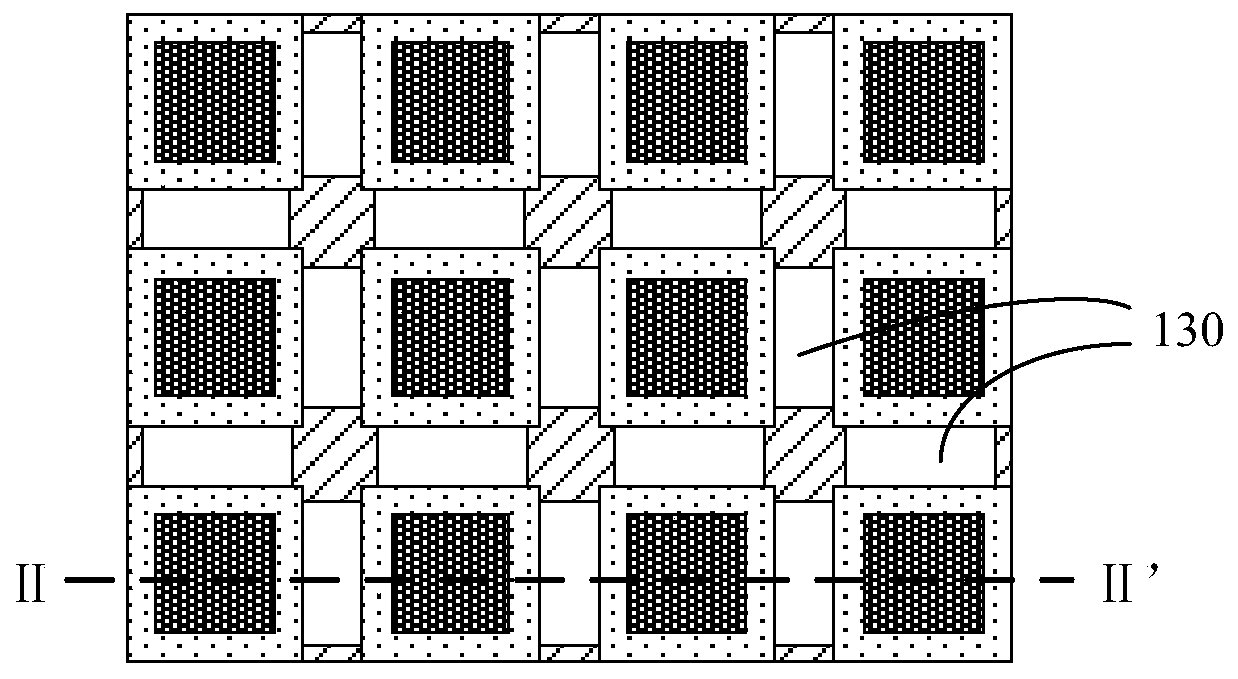

[0039] Refer below Figure 1A , 1B and Figure 2A , 2B , 2C, where Figure 1A is a schematic top view of a package substrate provided according to an exemplary embodiment of the present invention, Figure 1B is along Figure 1A The cross-sectional view taken along the line I-I', Figure 2A is a schematic top view of the package substrate obtained by the method according to the first exemplary embodiment of the present invention, Figure 2B is along Figure 2A The cross-sectional view taken along the line II-II'. Figure 2C yes Figure 2A A partial enlargement of the .

[0040] Next, specific implementations of the manufacturing method of the semiconductor device of the present invention will be described in detail.

[0041] First, a packaging substrate 100 is provided, the packaging substrate 100 has a first surface 101 and a second surface 102 opposite to each other, a plurality of chip prepackaging regions 110 are arranged on the first surface 101 and a plurality of c...

Embodiment 2

[0054] Refer below Figure 1A , 1B and Figure 3A , 3B ,in Figure 1A is a schematic top view of a package substrate provided according to an exemplary embodiment of the present invention, Figure 1B is along Figure 1A The cross-sectional view taken along the line I-I', Figure 3A is a schematic top view of the package substrate obtained by the method according to the second exemplary embodiment of the present invention, Figure 3B is along Figure 3A The cross-sectional view taken along the line III-III'.

[0055] Next, specific implementations of the manufacturing method of the semiconductor device of the present invention will be described in detail.

[0056] First, a packaging substrate 100 is provided, the packaging substrate 100 has a first surface 101 and a second surface 102 opposite to each other, a plurality of chip prepackaging regions 110 are arranged on the first surface 101 and a plurality of chips are located Strips 120 between the prepackaged areas.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com