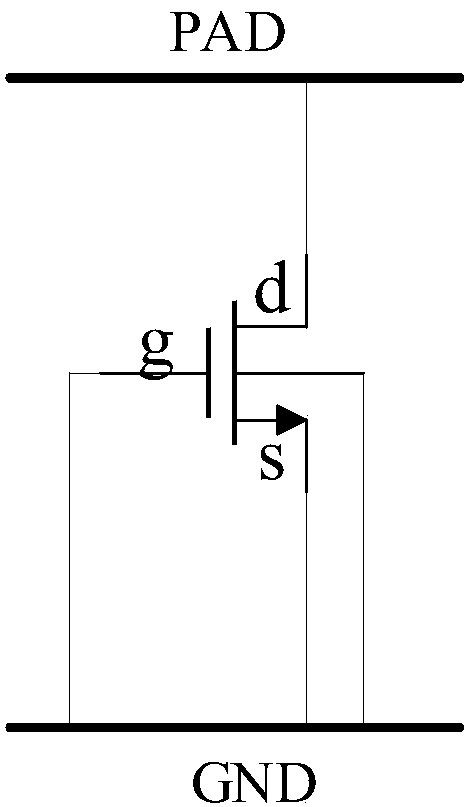

Electrostatic protection device based on SOI (Silicon-On-Insulator) technology and formed electrostatic protection circuit

An electrostatic protection and device technology, applied in the direction of electric solid devices, circuits, electrical components, etc., can solve the problems of small discharge capacity per unit size, insufficient ESD protection capacity, multi-layout area, etc., and achieve fast ESD response speed and reverse ESD The effect of enhanced protection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

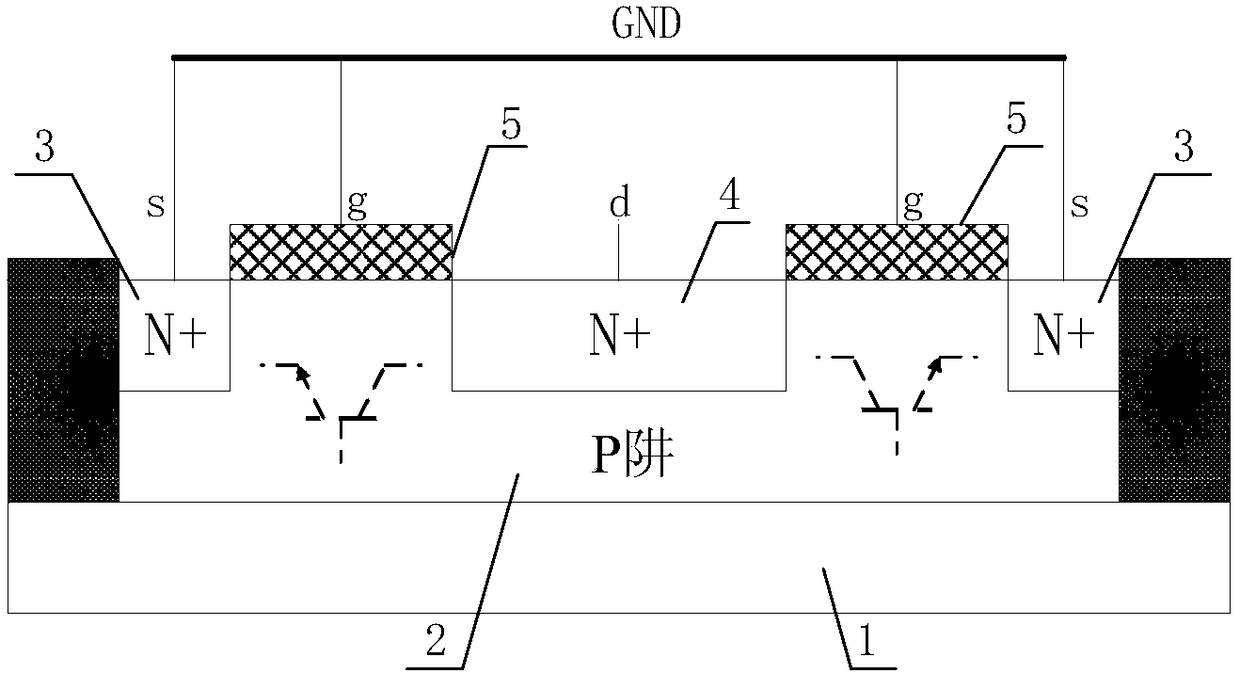

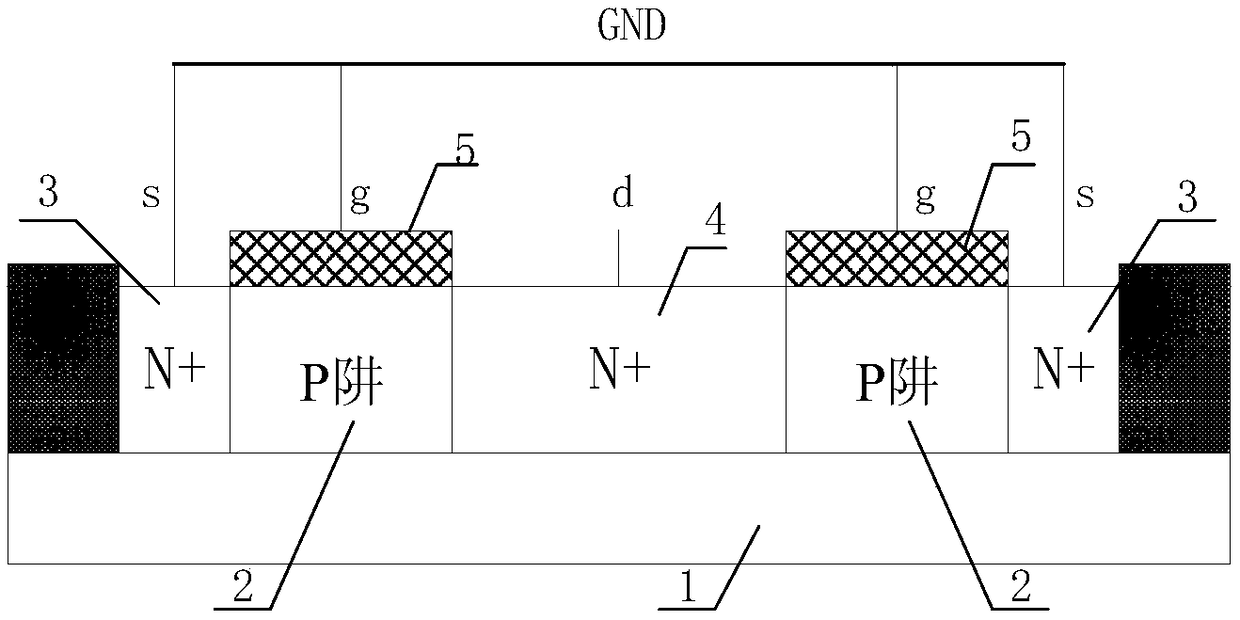

[0022] In order to make the present invention more comprehensible, preferred embodiments are described in detail below in conjunction with the accompanying drawings.

[0023] Figure 4 , Figure 5 Two embodiments of the improved electrostatic protection device of the present invention are given. and figure 2 , image 3 The structure comparison shows that the present invention adds a P+ contact region 6 and a dummy gate (dummy gate) 7 on the basis of the traditional multi-finger parallel GGNMOS. Wherein, the P+ contact region 6 is arranged on the side of the source 3 away from the drain 4, and the P+ contact region 6 and the source 3 are separated by the P well region 2; the dummy gate 7 covers the P+ contact region 6 and the source 3. on the P well region 2 between the source electrodes 3 . Since the P+ contact region 6 and the P well region 2 are connected, the P well region 2 can be electrically connected to the outside through the P+ contact region 6 (connected to GND...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com