Non-blocking parallel triangle rasterization unit structure

A unit structure and triangle technology, which is applied in the field of non-blocking parallel triangle rasterization unit structure, can solve the problems of GPU functions and performance cannot be fully utilized, commercial GPU chip replacement is fast, and the portability is poor, so as to improve the pixel generation ability and realize Effects of improved processing performance and scanning performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

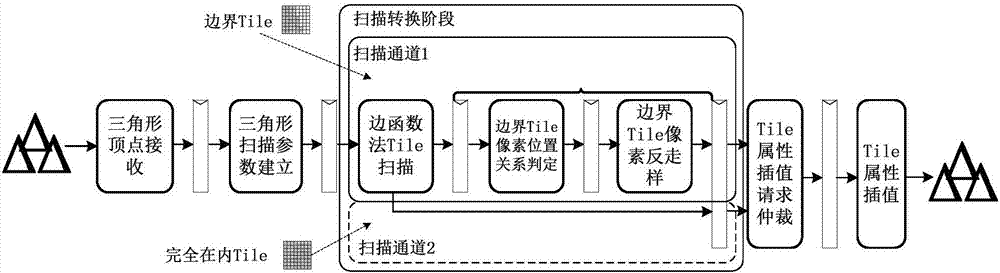

[0020] A non-blocking parallel triangle rasterization unit structure of the present invention is composed of 7 functional pipeline stages, and the 7 functional pipeline stages are a triangle vertex receiving unit, a triangle scanning parameter establishing unit, and an edge function method in sequence from front to back The Tile scanning unit, the boundary Tile pixel position relationship determination unit, the boundary Tile pixel anti-aliasing unit, the Tile attribute interpolation request arbitration unit and the Tile attribute interpolation unit are connected in order from front to back, and the data output of the previous pipeline level is used as the next one. Pipeline-level data input.

[0021] The triangle vertex receiving unit receives the vertex attribute transmission command sent from the outside of the rasterization unit, extracts the vertex attribute data in the command, stores it in the vertex attribute data buffer inside the unit, and then transfers the vertex at...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com