Fractional order delay realization method based on sampling control separation principle

A technology that separates principles and implementation methods, and is applied in adaptive control, general control systems, control/regulation systems, etc. It can solve problems that are not solutions, and achieve the effect of simple design, high resolution, and high fractional delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

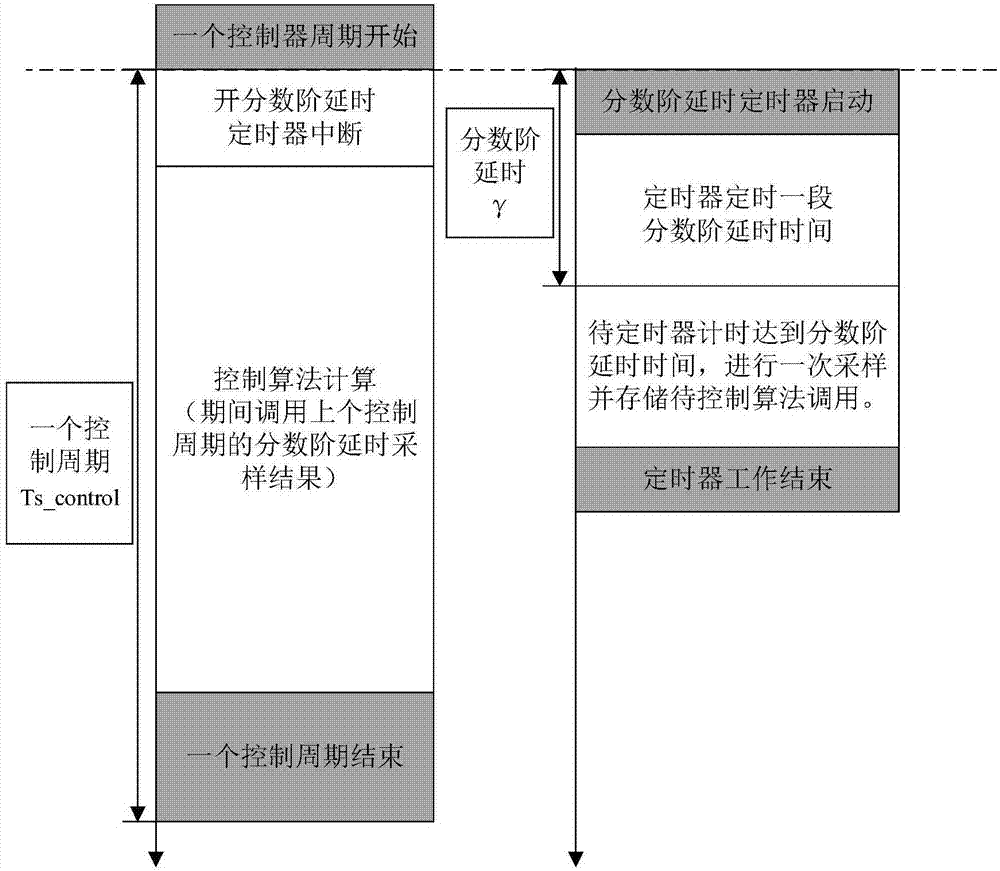

[0024] Specific embodiment one: for the digital control system that the fractional order delay link and the integer order link are connected in series

[0025] At a controller output update frequency f s_control In a 10kHz digital control system, if it is necessary to implement a 0.3 beat fractional delay link and the fractional delay link and the integer order part are connected in series, since the order of the series links of the control system can be exchanged, the This fractional delay link is equivalent to the fractional delay sampling of the input, that is, the input is 0.3*T s_control =0.3*1 / f s_control = 0.03ms delay sampling; set a f in the microprocessor timer = The 100kHz timer is used as a fractional timer, and the fractional timer is started at the beginning of each control algorithm cycle. The timing delay time γ of this timer is 0.03ms (three timer periods, 3*1 / f timer =3*T timer =3*0.01ms=0.03ms), that is, the timer counts three times; the fractional order...

specific Embodiment 2

[0026] Specific embodiment two: the numerical control system that is used for the digital control system that the fractional order leading link and the integer order link are serial relations

[0027] In some digital control systems (such as: repetitive controllers), it is necessary to realize the fractional-order lead link. If the fractional-order lead link and the integer-order link are connected in series, the realization of the fractional-order lead link can be converted into a fractional-order delay link. The realization of a digital control system with a fractional lead link, such as its controller output update frequency f s_control is 10kHz, it is necessary to implement a 0.3-beat fractional-order lead link, and this 0.3-beat fractional-order lead link is equivalent to a (1-0.3=0.7) beat fractional-order delay link and a 1-beat lead link, and the problem is transformed into input The 0.7 beat fractional delay sampling of the quantity, that is, the input quantity is 0.7...

specific Embodiment 3

[0028] Specific embodiment three: a digital control system comprising multiple fractional delay links and / or multiple fractional lead links

[0029] The present invention can also be applied to digital control systems with multiple fractional delays or fractional advances, where a controller outputs an update frequency f s_controlThe 10kHz digital control system includes a 0.3-beat fractional-order lead link, a 0.4-beat fractional-order delay link, and a 0.5-beat fractional-order delay link, and these three fractional-order links are connected in series with integer-order links, that is, three Each fractional-order link can be transformed into a fractional-order sampling of the input. Three fractional steps need to use three timers to trigger sampling. If the timer resources of the microprocessor are relatively tight, you can also put three delays in one timer, and then trigger three samples of the input. i.e. need delay γ 1 , gamma 2 , gamma 3 to trigger sampling, γ 1 =(...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com