Process for epitaxial growth of silicon in three-dimensional (3D) NAND flash structure

A technology of silicon epitaxy and flash memory, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the increasingly difficult three-dimensional memory cleaning process, affect the performance of channel preparation 3D NAND flash memory, and affect the quality of silicon epitaxial growth, etc. problems, to achieve the effect of avoiding etching damage to the interface layer, eliminating interface damage and lattice defects, good oxidation annealing and interface repair

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

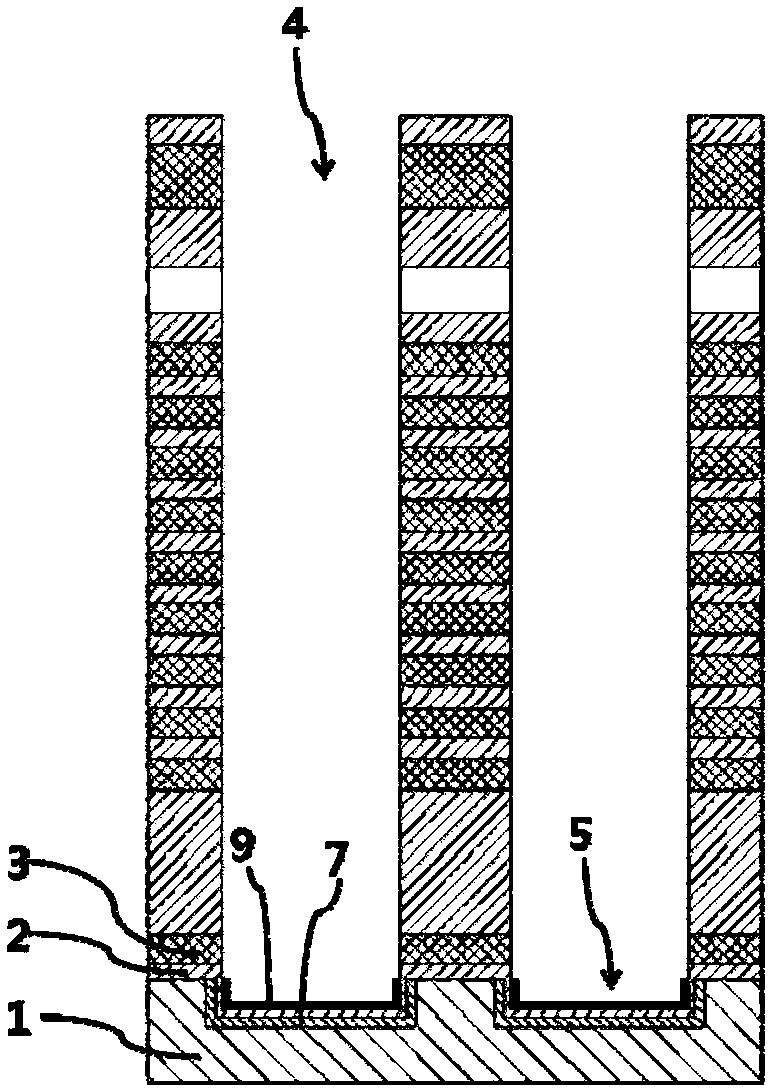

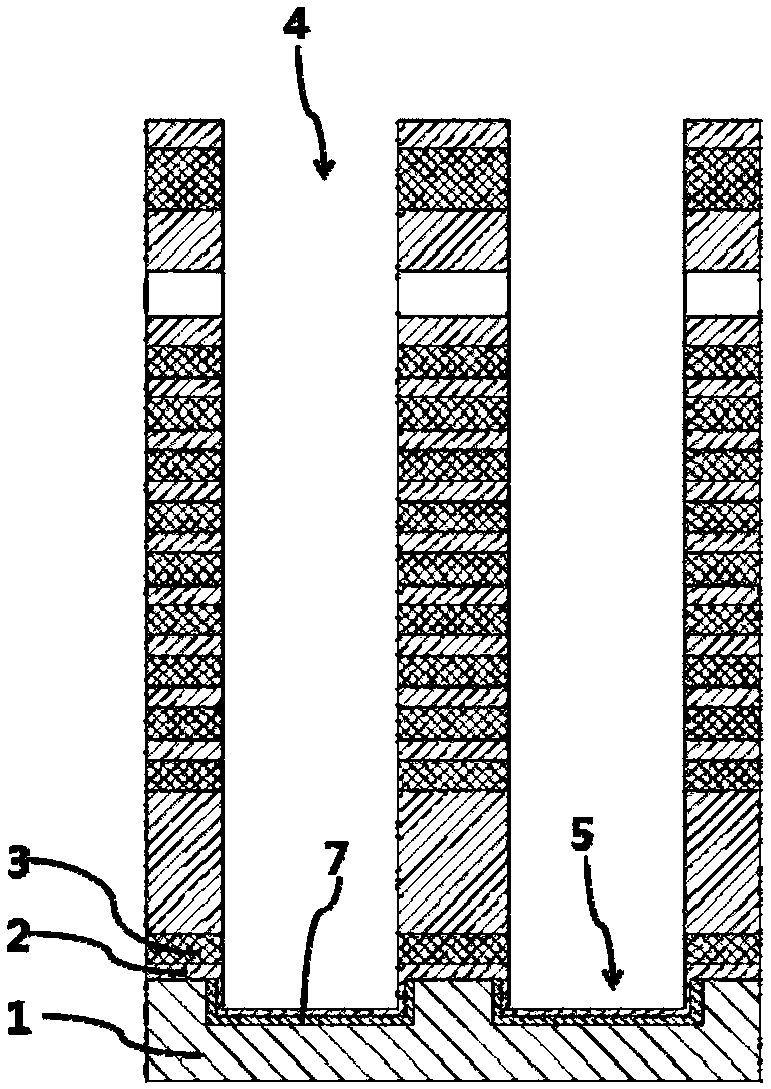

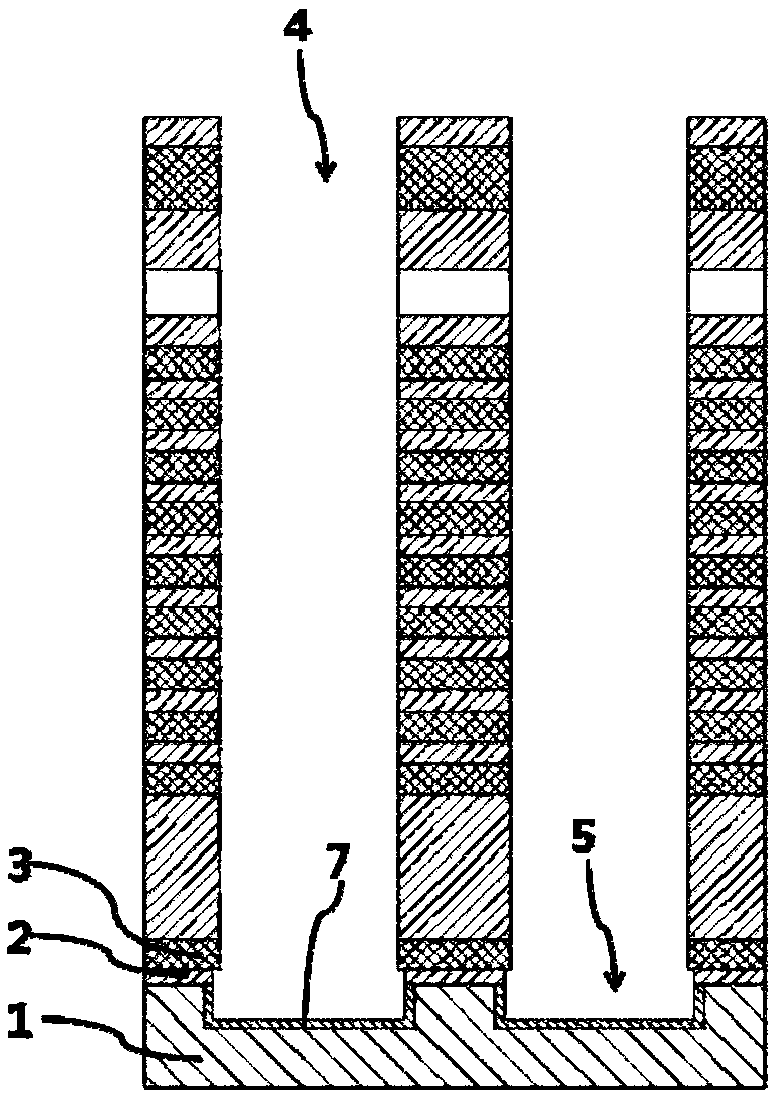

[0036] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

[0037] In the interest of clarity, not all features of an actual implementation are described. In the following description, well-known functions and constructions are not described in detail since they would obscure the invention with unnecessary detail. It should be appreciated that in the development of any actual embodiment, numerous implementation details must be worked out to achieve the developer's specific goals, such as ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com