A Method for Calculating the Area of Combined Figures in Electronic Layout

A technology combining graphics and electronic versions, applied in computing, computer-aided design, electronic digital data processing, etc., can solve the problems of easy omission or repeated calculation of calculation results, complicated calculation, inaccurate calculation, etc., to shorten the calculation time, application Wide-ranging, accurately calculated effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The invention provides a method for calculating the area of combined graphics of an electronic layout, comprising the following steps:

[0045] Step a, export the electronic layout as a GBR file in the EDA software for making the electronic layout;

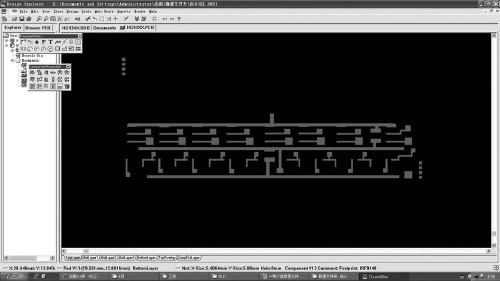

[0046] This embodiment takes PROTEL software as an example for specific description, such as figure 1 Shown is a gold conduction band single-layer printed pattern electronically laid out in the Protel environment.

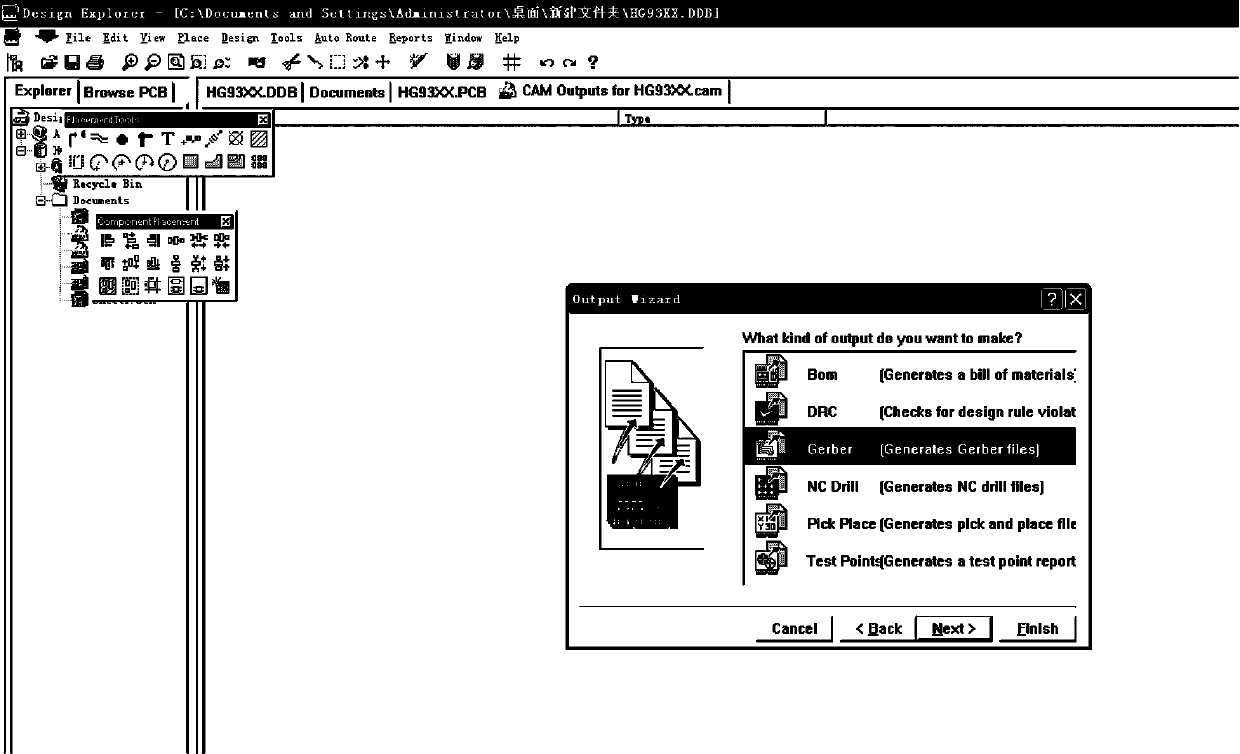

[0047] combine figure 2 As shown, enter Protel, open the PCB file, click File→CAM Manager in turn, in figure 2 Click "NEXT" in the pop-up menu, see the pop-up menu image 3 ,exist image 3 Select "Gerber" in the pop-up menu and then click "NEXT" continuously. When entering the graphics unit selection interface, generally select inch. When entering the layer selection interface, select the outer frame layer and the layer to be calculated. Continue to click "NEXT" continuously, and finally click "Finish"....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com