Semiconductor device with stacked layout

A technology for semiconductors and devices, applied in the field of semiconductor devices, can solve problems such as increasing difficulty, and achieve the effects of simplifying electrical connections and simplifying channel doping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

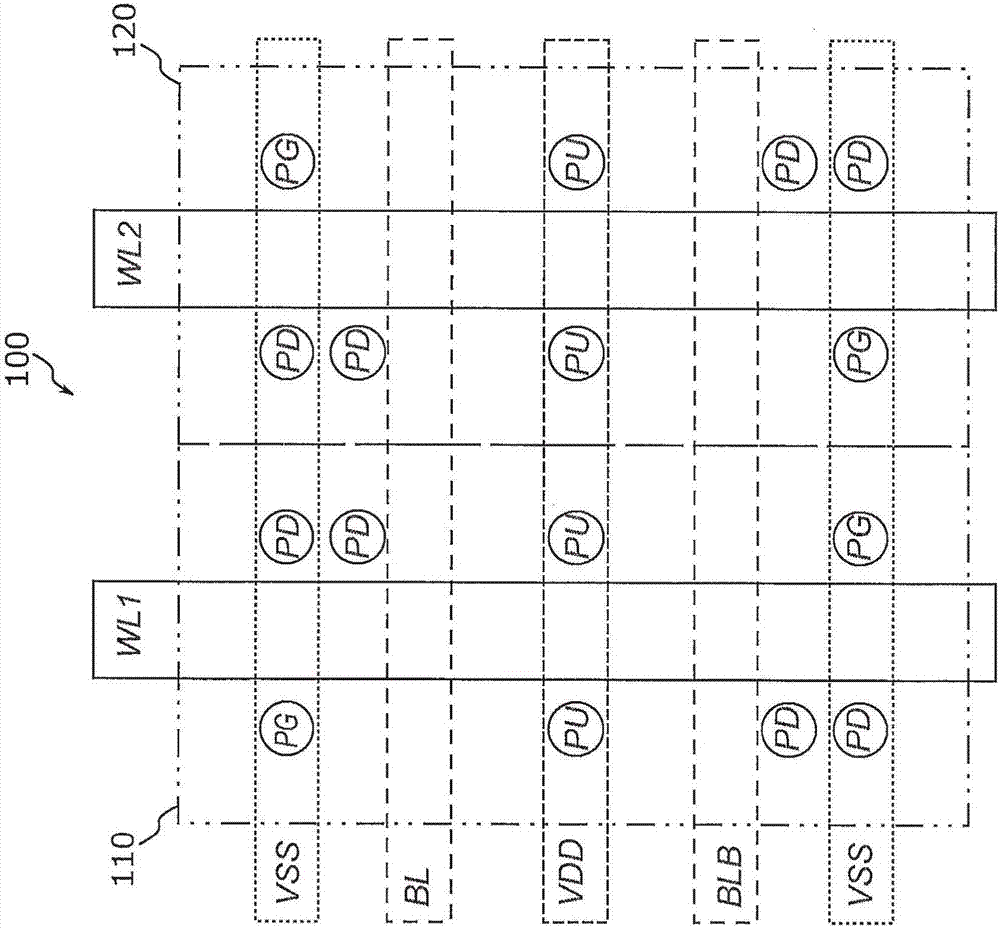

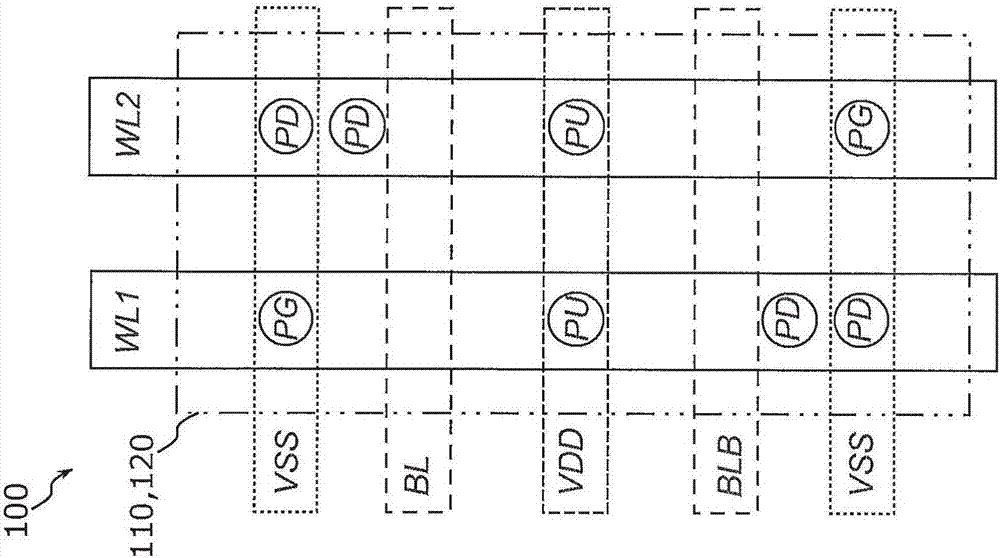

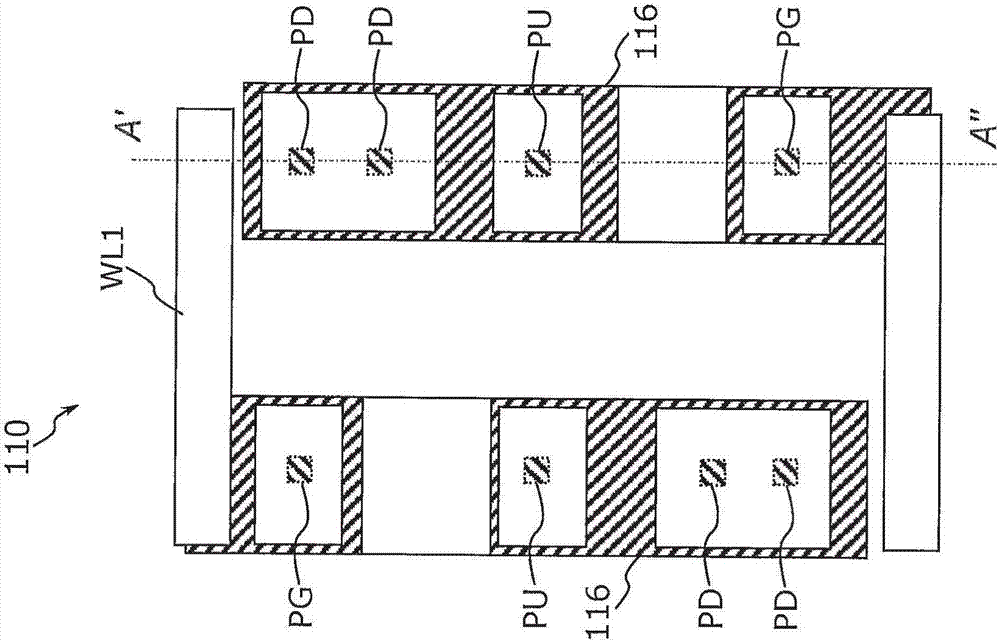

[0059] Detailed embodiments of the inventive concept will now be described with reference to the accompanying drawings. However, inventive concepts may be embodied in many different forms and should not be construed as limited to the embodiments set forth herein; Those skilled in the art convey the scope of the inventive concept.

[0060] The scalability of thin body devices (eg, fin transistors at the 5nm node and beyond) continues to pose challenges to maintaining acceptable performance parameters such as subthreshold slope (SS) and short channel effects (SCE). Gate-all-around (GAA) nanowire transistors (LFETs) can provide superior control of the gate over a fully depleted channel and allow the gate length to be further scaled by nanowires (NW) with a diameter of 4-7 nm. Scaled to 15nm. However, in conventional 2D layouts, gate length, sidewall spacers, and source / drain contacts compete for space within the pitch of the device. Additionally, ultrathin channels may also po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com