Hardware circular processing method and system of processor

A cycle processing and processor technology, applied in the direction of electrical digital data processing, instruments, machine execution devices, etc., can solve problems such as the impact of cycle efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention. In any processor or DSP, the design of circular cache can be completed according to the method provided by this design.

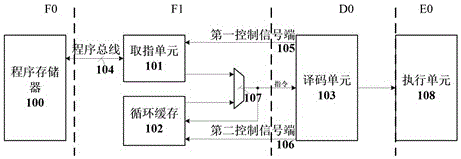

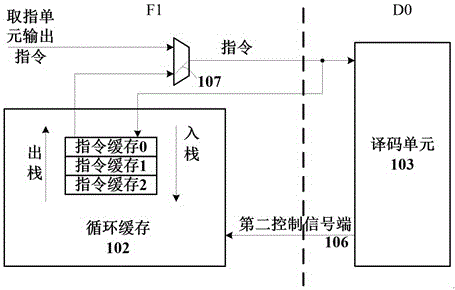

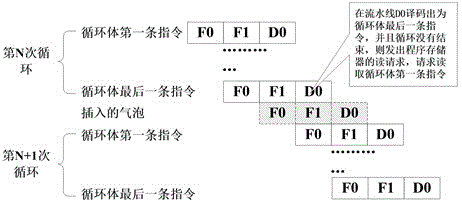

[0041] figure 1 It is a pipeline architecture diagram according to the present invention. The processor or DSP shown in the figure includes sequentially cascaded program memory 100 , instruction fetch unit 101 , decoding unit 103 and execution unit 108 respectively corresponding to the four-stage pipeline F0~E0 of the processor or DSP. F0 is the first-stage pipeline for instruction reading, and the instruction fetch unit 101 issues a read request for the program memory 100 at this stage of the pipeline. F1 is the second-level pipeline for instruc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com