Single-bus asynchronous serial port communication system and communication method thereof

An asynchronous serial port and communication system technology, applied in the field of communication, can solve the problems of low implementation efficiency and complex interface lines, achieve the effects of fast and accurate automatic detection, reduce complexity, and save chip costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

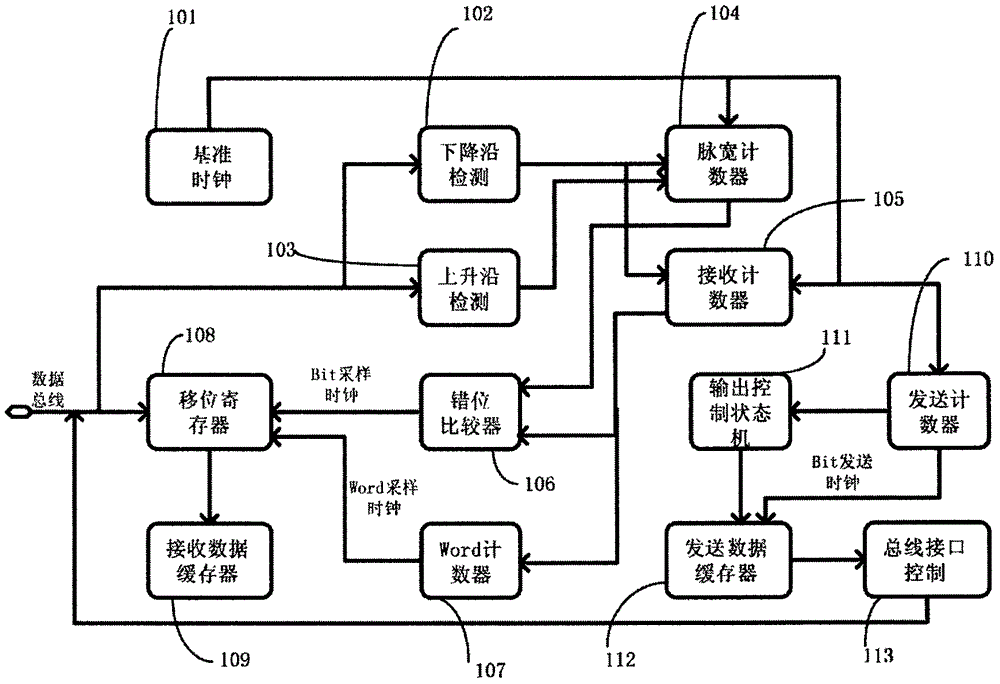

[0025] see figure 1 , in order to comply with a single-bus asynchronous serial communication system described in this embodiment, including: a master device and a slave device, the master device and the slave device are connected through a data bus, and the slave device has a built-in There is a serial port communication interface circuit, which realizes automatic detection and adjustment of the baud rate of the master device, accepts control commands and data from the master device, and returns corresponding response data.

[0026] Preferably, the serial port communication interface circuit includes: a rising edge detection module, a falling edge detection module, a pulse width counter, a receiving counter, a shift register, a misalignment comparator, a receiving data buffer, and a word counter, wherein the rising edge detection module, the falling edge detection module, and the shift register are all connected to the data bus for receiving data sent by the data bus; the risi...

Embodiment 2

[0031] A communication method based on the single-bus asynchronous serial port communication system described in embodiment 1, comprising the steps of:

[0032] Baud rate automatic detection steps: After power-on, the master device sends OX01 data to the slave device, and the slave device calculates the current communication baud rate by detecting the width between the first falling edge and the first rising edge on the data bus; Specifically, a pulse width counter is used to start counting from the falling edge and stop when the rising edge comes. The clock of the counter comes from the reference clock signal inside the circuit, and the frequency of the clock signal is much higher than the baud rate. The data recorded by the pulse width counter represents the current baud rate, and the pulse width counter will be locked after the first count, and will not be triggered by the falling edge of the data line to count again, unless the system is reset or the host sends baud rate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com