Multilayer SOI material and preparation method thereof

A H2SO4, underlying technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as poor quality of silicon wafers, stacking restrictions on the number of layers, edge bonding of silicon wafers, etc., and achieve the effect of small edge loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

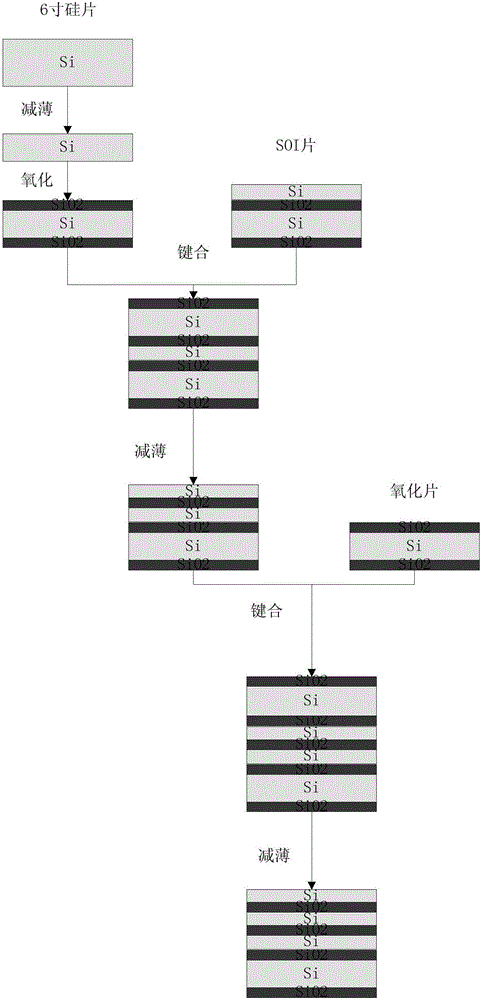

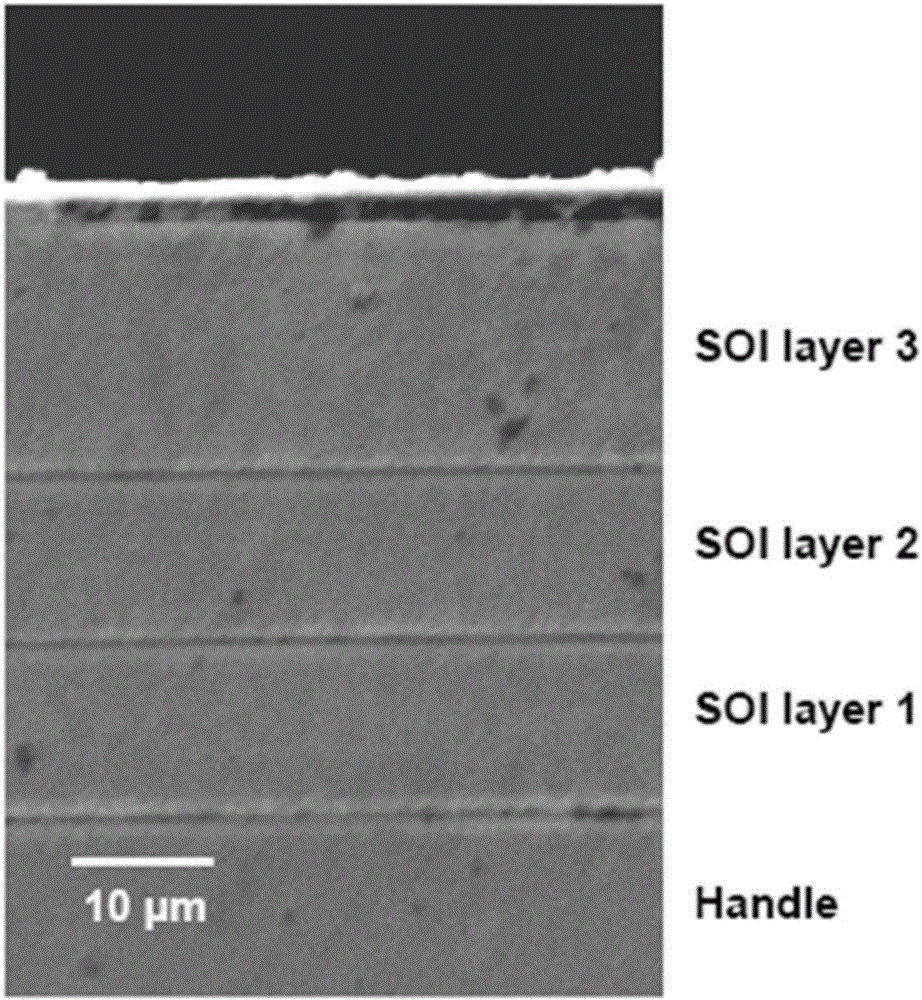

[0034] This embodiment is the preparation of 6-inch 3-layer SOI material, and the process is as follows ( figure 1 ):

[0035] (1) Take a 6-inch, N-type, resistivity 4-7ohm.cm, crystal orientation silicon wafer, and thin it to 400μm. Then oxidize, the oxide layer is 0.5μm.

[0036] (2) Choose a piece of 6-inch SOI: the top silicon thickness is 10μm, N type, resistivity 8-12ohm.cm, crystal orientation ; the middle oxide layer silicon dioxide is 0.5μm; the substrate silicon thickness is 675μm, N Type, resistivity 8-12ohm.cm, crystal orientation .

[0037] (3) Carry out CMP stress relief treatment (treatment time 180 seconds, polishing pressure 20KPa) to the oxide layer on the silicon chip in step (1), then carry out 3min surface treatment with DHF, carry out plasma activation again (using N 2 , gas pressure 0.3mbar, activation time 5s, RF power 75W). Use concentrated H on the SOI sheet of step (2) 2 SO 4 Treat at 120°C for 3 minutes without plasma activation; then bond th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Layer thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com