Calibration algorithm applied to time-interleaved analog-to-digital converter

An analog-to-digital converter and time interleaving technology, applied in the direction of analog-to-digital converter, analog/digital conversion calibration/test, etc., can solve the problems of poor calibration effect and high logic resource consumption, saving loss, reducing complexity, The effect of real-time calibration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

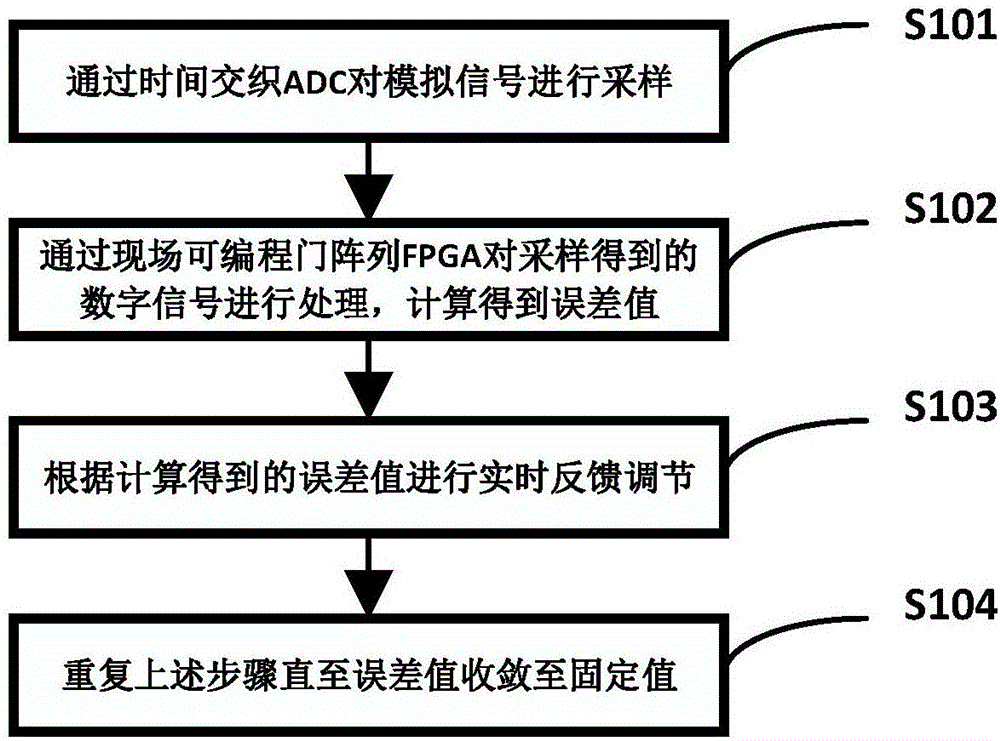

[0034] The invention discloses a calibration algorithm applied to a time-interleaved analog-to-digital converter, which mainly adopts off-chip calibration technology, such as figure 1 shown, including the following steps:

[0035] Step S101, sampling the analog signal through the multi-channel analog-to-digital converter ADC;

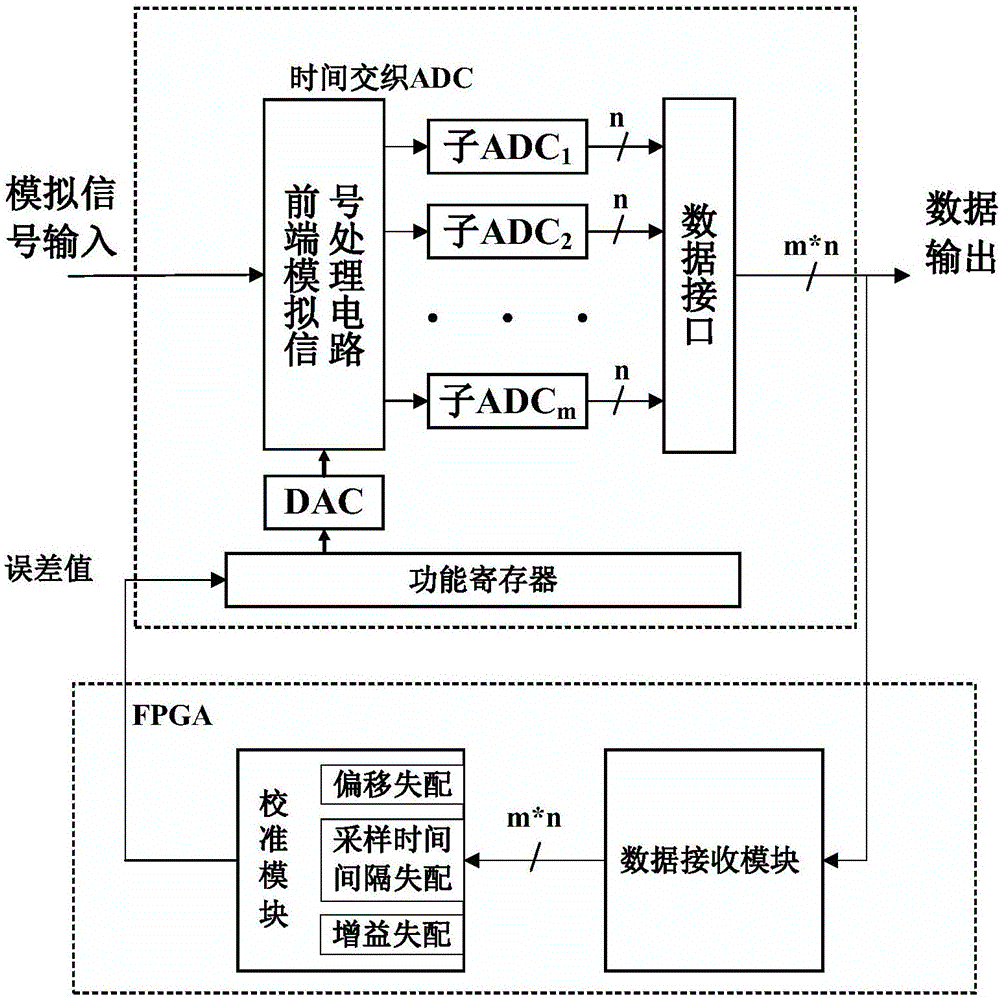

[0036] Specifically, in this embodiment, as figure 2 As shown, the multi-channel sub-analog-to-digital converter ADC of TI-ADC can be used 1 、ADC 2 and ADC m Single-frequency sine waves are sampled separately, but in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com