FPGA-based clustering algorithm acceleration system and design method thereof

A technology for accelerating systems and clustering algorithms, applied in program control design, computing, instruments, etc., can solve problems such as slow access to off-chip memory, achieve extensive clustering problems, reduce the number of times, and achieve good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

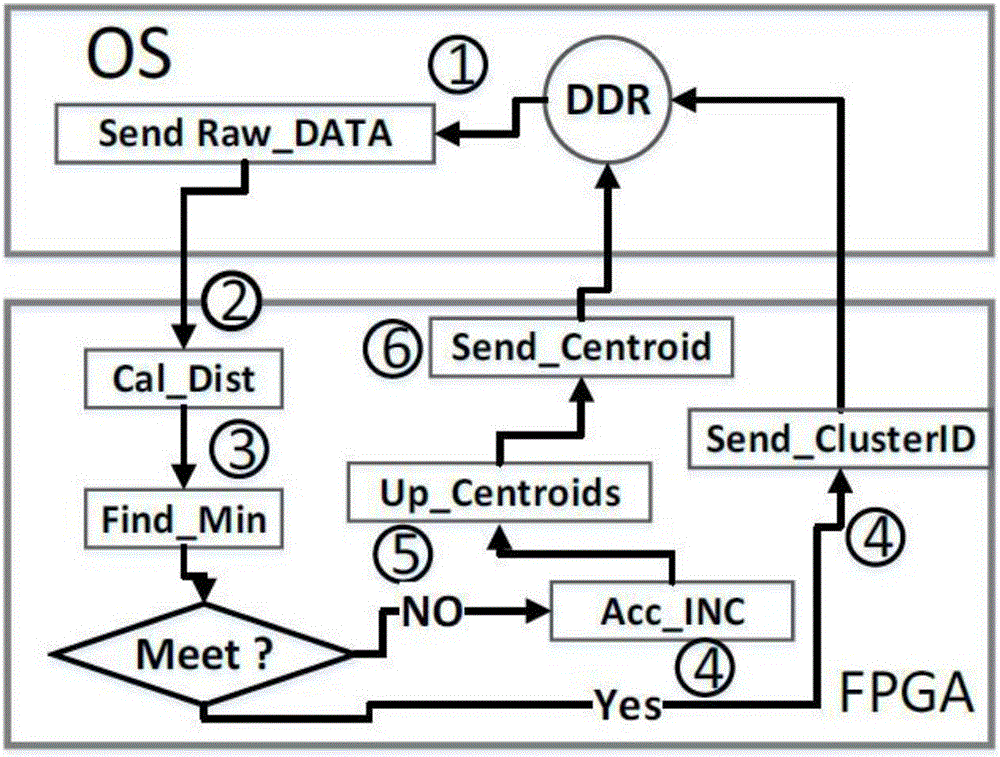

[0054] The clustering algorithm accelerated by the acceleration platform in the embodiment of the present invention is Kmeans, PAM, SLINK, DBSCAN algorithm, and each kind of algorithm supports the standard of two kinds of similarity measures of Manhattan and Euclidean; The acceleration platform refers to Field Programmable Gate Array (Field Programmable Gate Arrays, referred to as "FPGA") and a general purpose processor (General Purpose Processor, referred to as "GPP") computer system, where the general purpose processor includes a central processing unit (Central Processing Unit, referred to as "CPU"), network Processor (Network Processor, referred to as "NP") and the like.

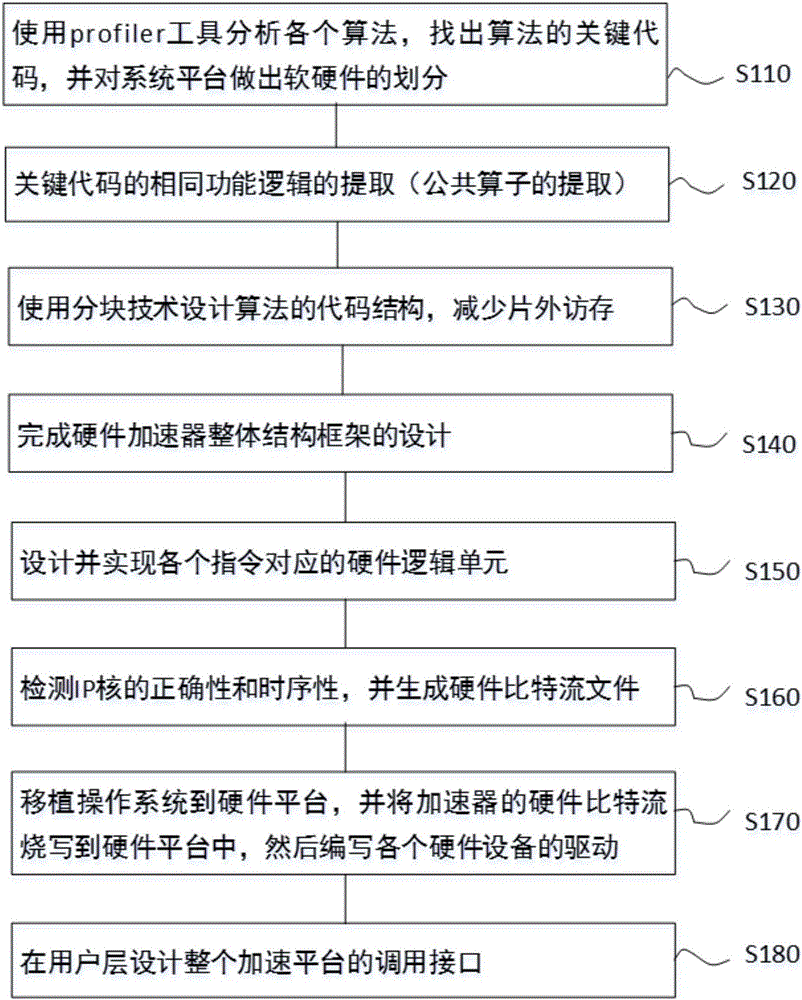

[0055] figure 1 It is a design flowchart of the acceleration system platform of the embodiment of the present invention; the design steps included are as follows:

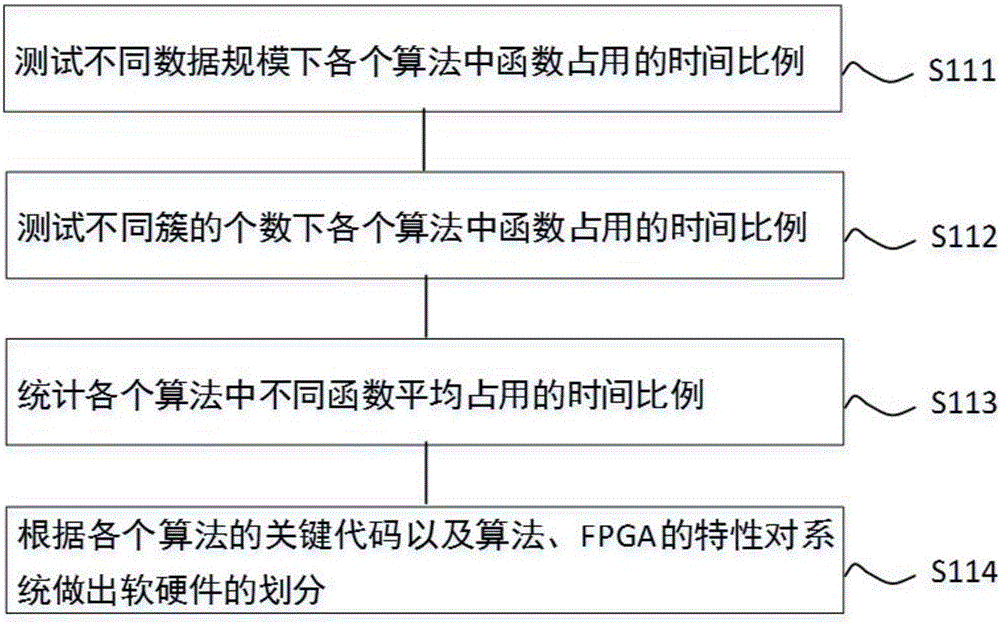

[0056] The software and hardware division tasks of the acceleration system S110, the specific division work is in figure 2 Detailed steps...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com