A dielectric isolation structure and method for SOI process

A dielectric isolation and process technology, applied in electrical components, transistors, circuits, etc., can solve the problems that the shallow trench isolation technology cannot meet the circuit requirements, high complexity, and the difficulty of the full dielectric isolation process, so as to improve the resistance to total dose radiation. Lighting ability, small impact, avoid long-term high temperature annealing effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Below in conjunction with accompanying drawing and embodiment, describe technical solution of the present invention in detail:

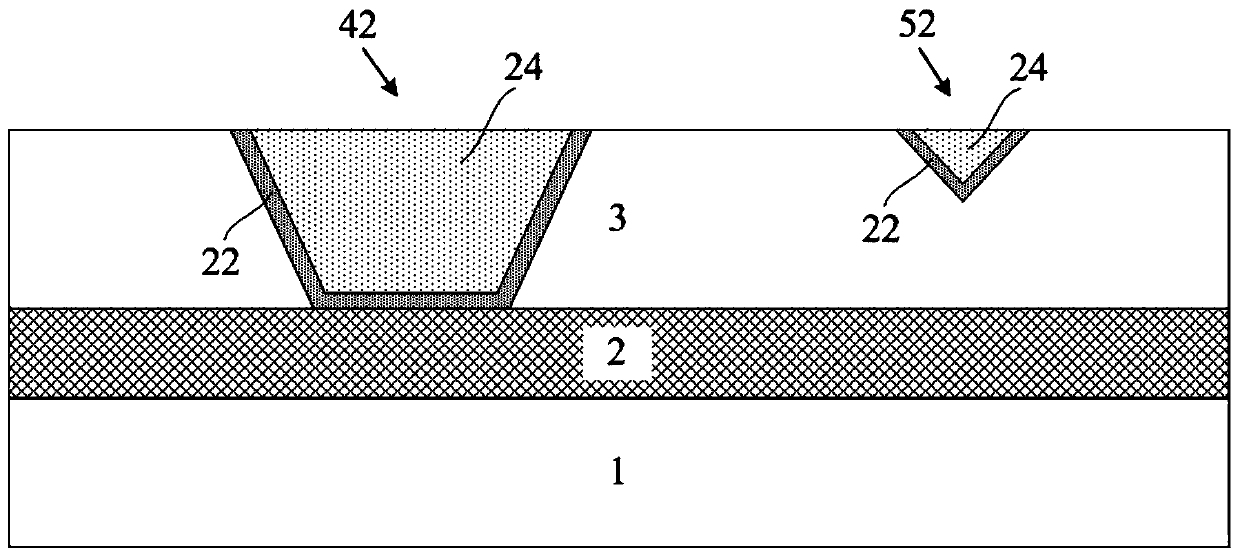

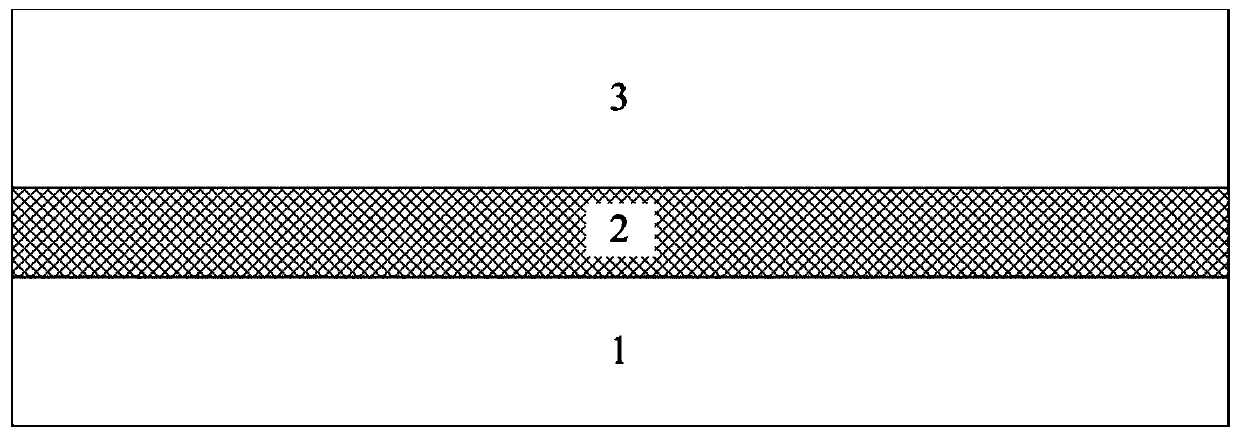

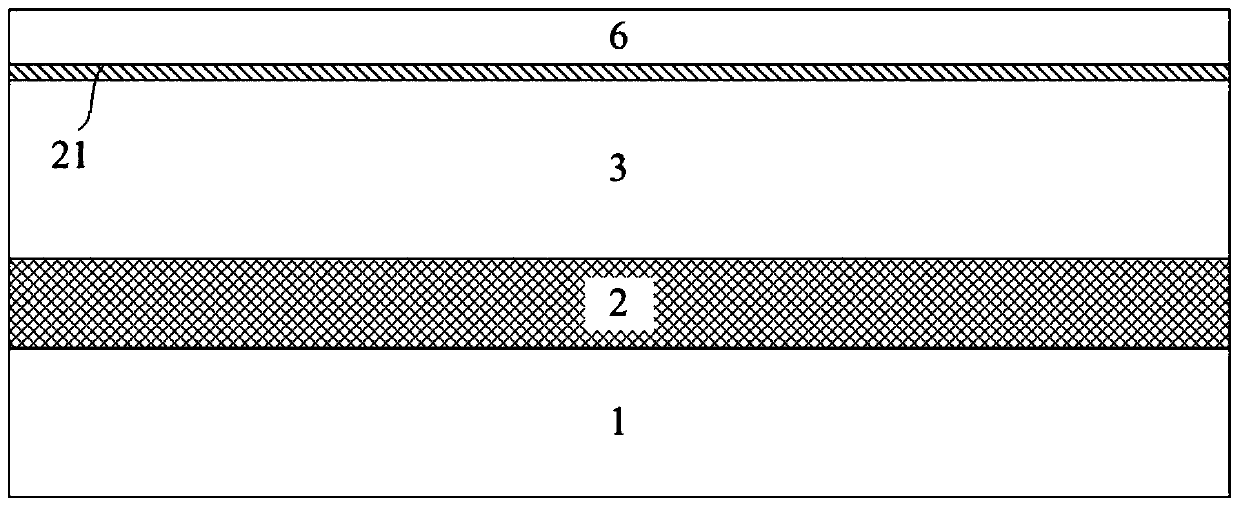

[0041] Such as figure 1 As shown, a dielectric isolation structure for SOI process of the present invention includes a P-type substrate 1, a buried oxide layer 2, an SOI material top layer silicon 3, a full dielectric isolation trench 42, a partial dielectric isolation trench 52, and a linear oxide layer 22. The oxide layer 24, the full dielectric isolation trench 42 and part of the dielectric isolation trench 52 are located in the top layer silicon 3 of the SOI material, above the buried oxide layer 2, the linear oxide layer 22 is located between the full dielectric isolation trench 42 and part of the dielectric isolation trench 52 On the inner surface, the oxide layer 24 is surrounded by the linear oxide layer 22 and is located inside the full dielectric isolation trench 42 and part of the dielectric isolation trench 52 , while the linear ox...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com