Wafer-level package mems chip with vertical pads and manufacturing method thereof

A wafer-level packaging and manufacturing method technology, applied in the field of MEMS chips, can solve the problems of high cost and complicated process, and achieve the effect of convenient subsequent packaging and simple operation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

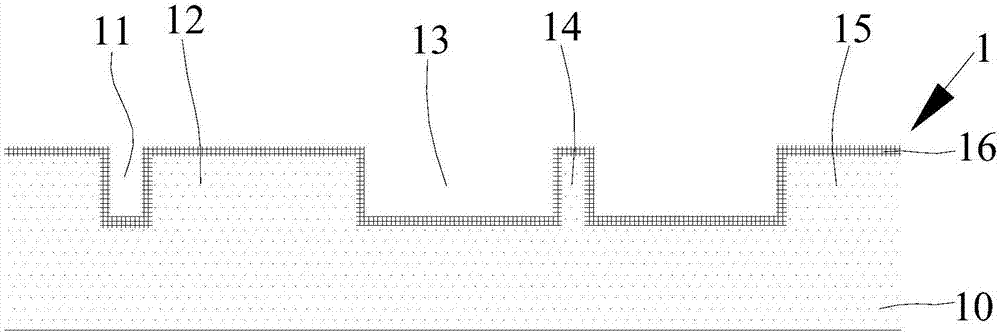

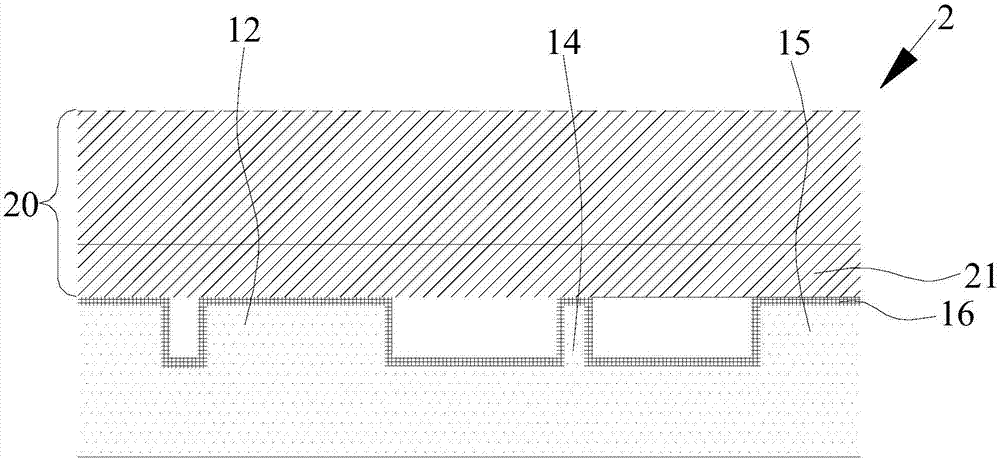

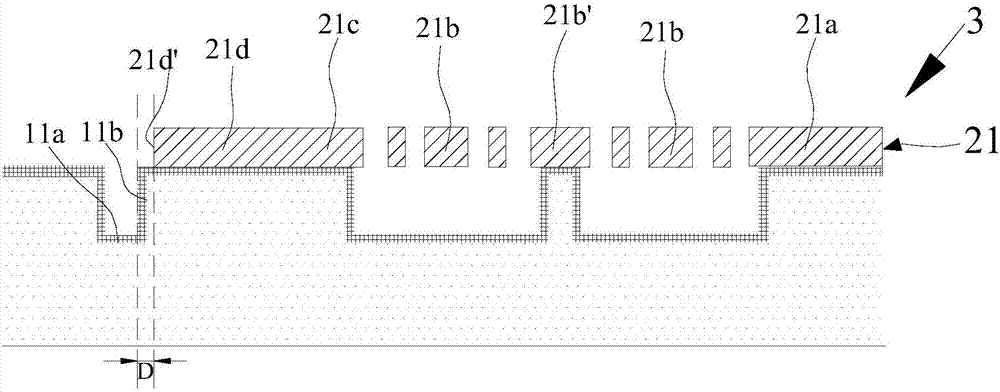

[0031] A method for manufacturing a wafer-level package MEMS chip with a vertical pressure welding block, comprising the following steps:

[0032](1) Fabrication of base plate wafer 1: use double-sided polished single-crystal Si wafer 10 as the base plate material, and after photolithography process steps such as coating photoresist, alignment, exposure, and development (hereinafter referred to as photolithography), A photoresist pattern is formed on the double-sided polished single-crystal Si wafer 10, and the photoresist pattern is used as a mask for deep Si reactive ion etching (DRIE), and Si is etched in a reaction atmosphere containing fluorine (F), and the reaction The gas used is usually SF 6 and C 4 f 8 , where SF 6 is the isotropic etching gas, C 4 f 8 is the gas that produces polymers, alternating SF in reactive ion etching equipment 6 and C 4 f 8 , etch a 50-200 μm deep pattern on a double-sided polished single-crystal Si wafer 10, remove the photoresist, an...

Embodiment 2

[0045] The fabrication method of the wafer-level package MEMS chip 7 with vertical pads in this embodiment is similar to the fabrication method of Embodiment 1, the only difference is that step (1) also makes chamfers 11c on the top of the bottom groove 11, An insulating layer 16 is also grown on the chamfer 11c; step (4) also deposits a metal layer 34 on the insulating layer 16 on the slope of the chamfer 11c, and due to the existence of the chamfer 11c, it is also beneficial to the metal layer 34 in step (4). 34 evenly covers the chamfer 11c slope and the bottom plate groove side 11b.

[0046] The difference between the wafer-level package MEMS chip 7 with vertical pads produced in this embodiment and the wafer-level package MEMS chip 7 with vertical pads produced in Embodiment 1 is only that the top of the groove 11 on the bottom plate has a chamfer 11c, the metal layer 34 is also deposited on the slope of the chamfer 11c, such as Figure 12 shown.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Depth | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com