Jitter control circuit within chip and associated jitter control method

A technology for controlling circuits and chips, which is applied in automatic control of power, control/regulation systems, and measurement of electricity, etc., and can solve problems such as supply voltage noise, severe jitter clocks of clock generators, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

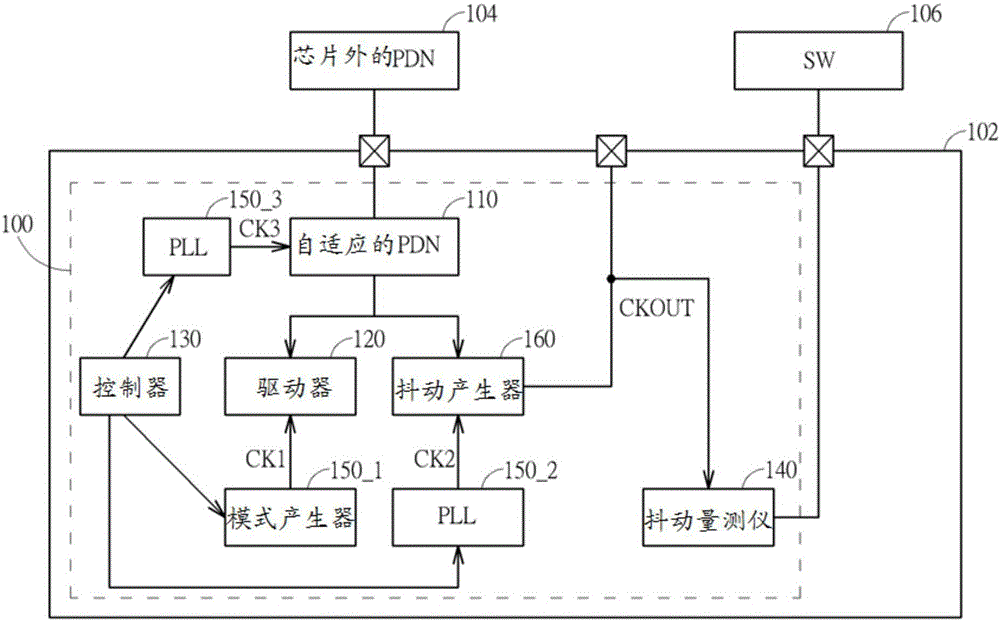

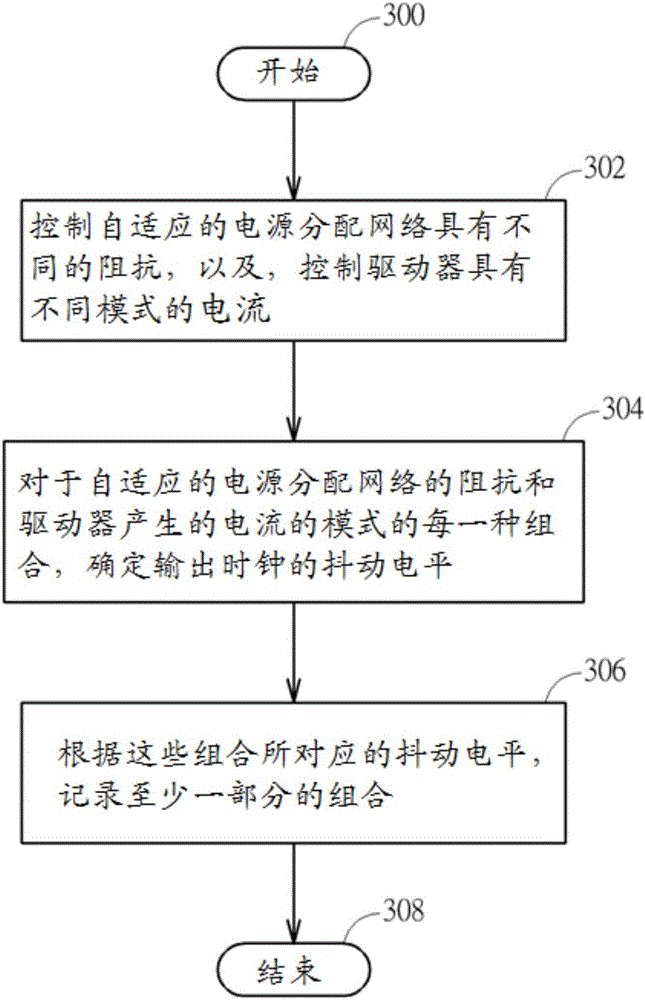

[0013] The following descriptions are preferred embodiments of the present invention, and these preferred embodiments are only used to illustrate the technical features of the present invention, rather than to limit the scope of the present invention. Certain terms are used throughout the specification and claims to refer to particular elements. Those skilled in the art should understand that the manufacturer may use different terms to refer to the same component. Therefore, this description and the claims do not use the difference in name as a way to distinguish components, but the function of the components. difference as a basis for distinction. The terms "element", "system" and "apparatus" used in the present invention may be a computer-related entity, where the computer may be hardware, software, or a combination of hardware and software. The terms "comprising" and "including" mentioned in the following description and claims are open terms, so they should be interpreted...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com