Cooling structure of package chip

A heat dissipation structure and chip technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of distance error, affecting chip performance and service life, slow emission, etc., and achieve the effect of overcoming installation errors and improving EMC performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present application will be further elaborated below in conjunction with specific embodiments. It should be understood that these examples are only used to illustrate the present application and are not intended to limit the scope of the present application.

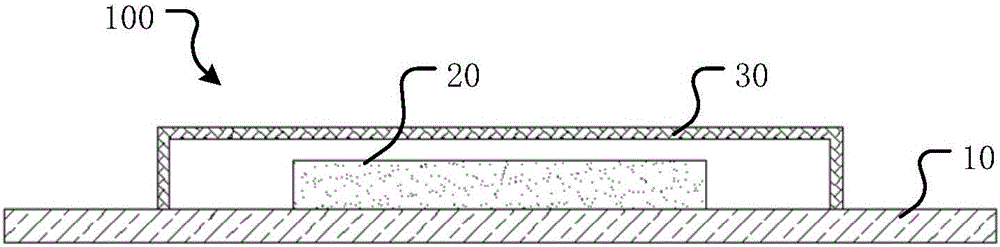

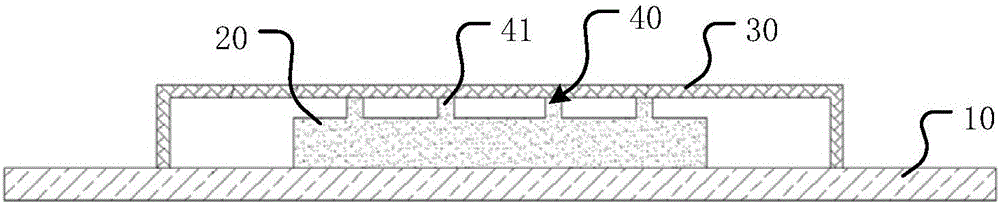

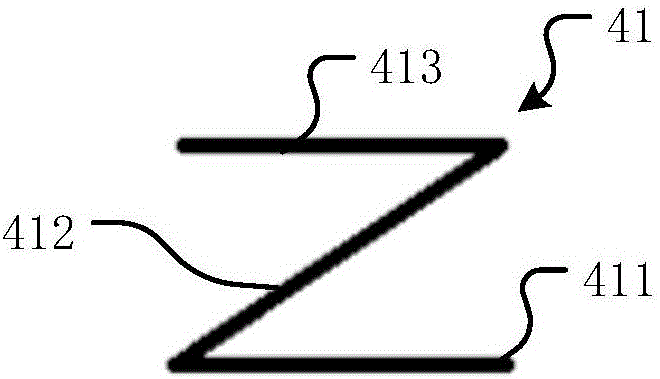

[0028] Such as figure 2 As shown, the heat dissipation structure 100 for packaged chips in one embodiment of the present application generally includes a PCB board 10, a chip 20 mounted on the PCB board 10, a shielding case 30 packaged on the PCB board 10 and covering the chip 20, And the heat sink 40 is arranged between the upper surface of the chip 20 and the lower surface of the shielding case 30 and has an elastic movable range.

[0029] Through the elastic heat sink 40, the height error between the chip 20 and the shield 30 can be completely overcome, so that the heat can be transmitted to the shield 30 through the heat sink 40 as soon as possible, and then dissipated by the external heat dissipation co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com