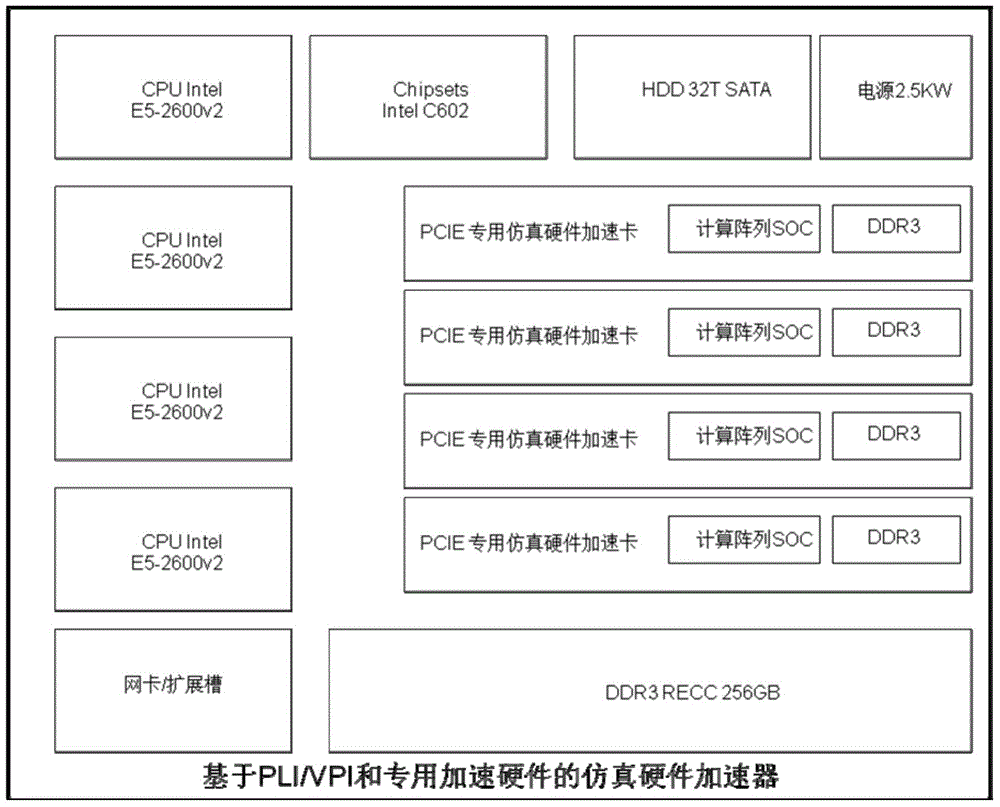

Simulation hardware accelerator based on PLI (Private Line Interface)-VPI (Virtual Path Identifier) and special acceleration hardware

A technology of hardware accelerator and dedicated hardware, which is applied in the field of simulation verification accelerator, can solve problems such as shortening simulation time, achieve the effects of shortening simulation time, reducing simulation complexity, and improving simulation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The invention will be further described below in conjunction with specific embodiments.

[0016] As shown in Figure 1, the present invention is made up of central processing unit CPU, motherboard chipset, memory, hard disk, optical drive, power supply, expansion port, special-purpose hardware acceleration card PCIE card. Described central processing unit CPU comprises 4wayCPU; Described special-purpose hardware accelerator card is provided with PCIE interface, SOC chip, DDR3 memory; Described special-purpose hardware accelerator card comprises 4way special-purpose hardware accelerator card, forms SOC computing array; Described power supply is central processing CPU, motherboard chipset, memory, hard disk, dedicated hardware accelerator card power supply. The central processing unit CPU is E5-2600. The motherboard chipset is ChipsetsIntelC602 chipset. The memory is 256GB RECC memory. The hard disk is a 32T hard disk memory. The power supply is a 2.5KW power supply. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com